FIRME TRADEDART REPART OF DE Introduction :-In whit i we discuss about the Lopic OF Jupoduction to pic microcontroller so Pic 16(6x, 6 pic 16(+x Architecture and its expanations to pic 16cxx - to the pilering process to the program memory considerations to the File Structure (in) Register File abricture to the instruction set and the addressing operations. In unit ? we are going study about the Navious Intervipts a Pic micro componer inton-Pts to its types ((e) External in Lenvort to bus

Timers Pic micro connect in Lewist » its LARS (10) External in Lewist » its LARS (10) External in Lewist » Tolenat programming is the loss timers - Timer native is the Varias timers - Timer active is the Trant Parel I/6 - SoFt 3 Programming is Trant Parel I/6 - SoFt 3 Programming is Constant is Variable strings 3 SP104 OF Constant is Variable strings 3 SP104 OF Line inter Facing In unit ? we discuss about In unit ? we discuss about In unit ? we discuss about 1 PaiPherals is the inter Facing

The Bos For peripender chip Acres to ibbe bus operation. Bus subroutines to Serial Eprom.

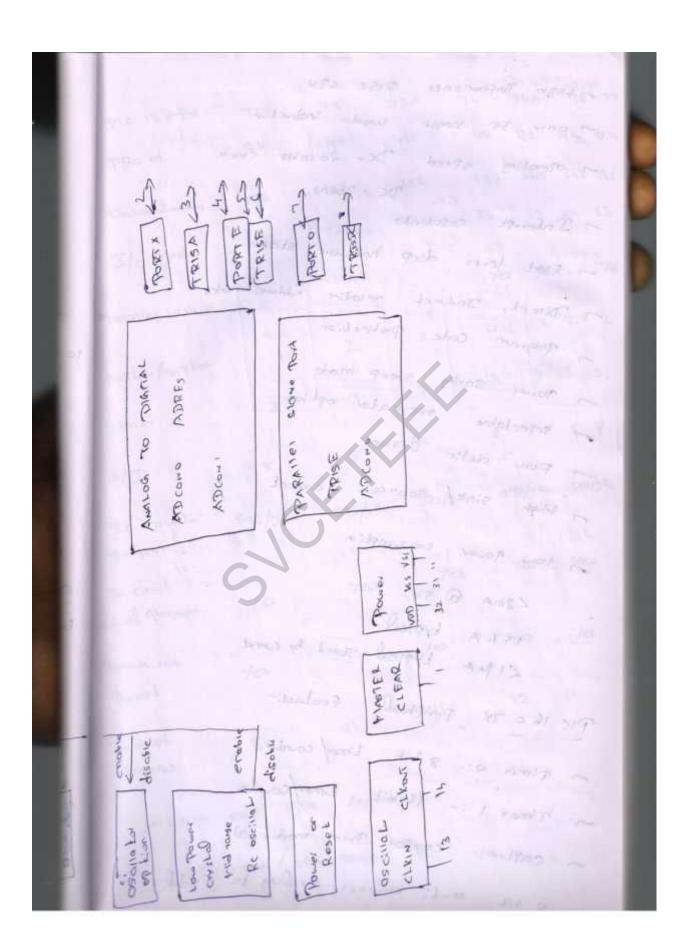

Andlog to Digital convert a UMRT to the Band rate selection to the data handling circuit to the initialization and the keyboard interfacing & In the LCD to the sensor interFacing. Jo unit f we discuss about the Chir Life ADC. DAC 10 199 1-1-AT In Londuction to Arm processor to the 1.5 processor to anditedure of Am Programmers moder to the deveropment of 10 Avm bools and the memory 15 programming. lang lage to the Ann Assembly Co tourpies also we are discuss about the architectural support A SIRE SIMPLE 0 Fox interior (10) Island 20 operating systems about the we dis cuss Ann organization to the 3stage pine line Aim organization. The 5 stage pipe line Arm organization, the Arm instruction process, Arm implementation to Arm Coprocessor execution instruction set to Avm co Processor the and the Architectural support for Higher level lang yages to RAM Applications.

anit - I - Introduction to Tic Microcontinent Pic Shands Tox Peripheral Later most Interface controller brain child of prices Chip Lechnology, USA support device For PDP computors to control perphered devices, named as PIC . Single Chip micro controller 8-bit micro conbrollers have now a days in industry automation. earlier version of Pic microcontroller is sic 16 c BX/TX. TX- malos to digital Converter capability. Micro controller are available with varge of capabilities packed in both dual in line Packages Packages Surface mount Parkages part number used that Pic . out Tealure 14 2.0 incude procure Amos at as operate at its maximum clock rate. speed: -Pic execute most of its instruction in 0.2 45 Instruction set simplicity: set consist OF Just 35 Instiction set Instruction Integration of operational reautures: -Power or reset bown out pulaction

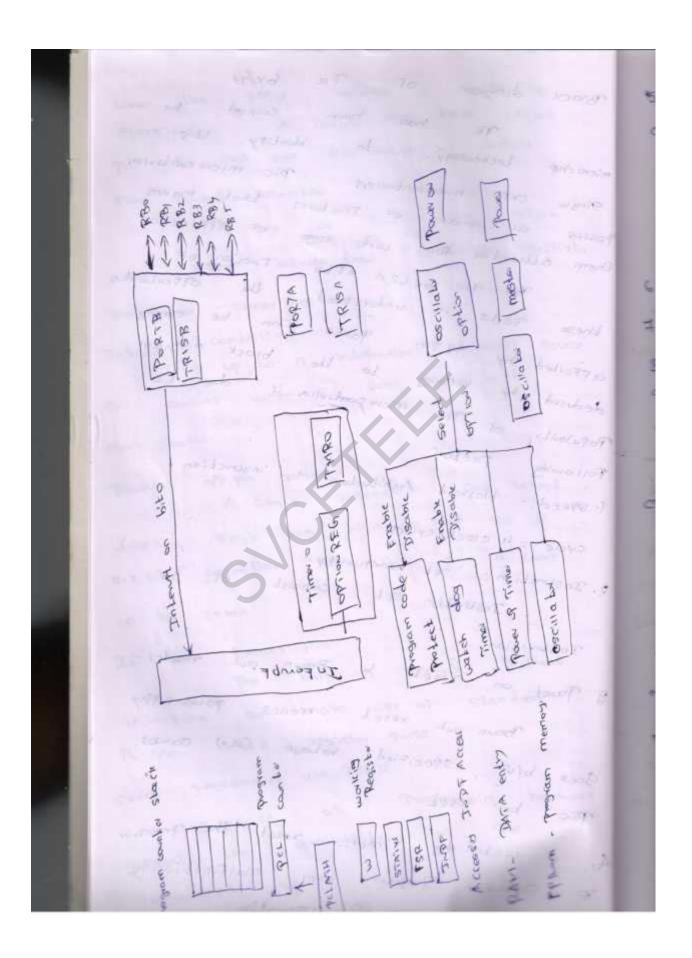

Brock diagram OF Pic 6x/1x. Tic has been coined by microchip Lechnology. Lo identify its Single Chill micro comboliers Pic micro con boller Posses an anay of Features that makes them alliactive for uside range of apprication. The Mic 166621 AFter Function OF these parts is understood the opportunities afforced by 18 Pin Parks Can be easily deduced by refering to the block diagram. Popularity of Pic microcontrolia is Following Factors 1. speed: - Harvard Architecture 1, instruction CYCLE = 4 CHOCK CYCLES. 2. Instruction :- Set simplicity: Instruction Set Consist of 35 Instruction. & Pauer on reset to Brown out reset: -Boun out reset means power supply goes b/w specified vollage (a) causes The bo reset. 4. A watch dog timer: reset the processor if software Program ever malfunction 1

5. Pic micro controlles have Four optional 343 V Sources . Clock Low Power crystal tild varge crystal High varge crystal Re oscillator 6. Program Emois to on chip Micup to R independent interat spirices 1 3 PowerFor olp Fin control 9. EPROM OTP/Rom/Flach memory ortion to 3/0 Port expansion carabitly 11. Tree assembler to similate support copu negisters working register 0 RPO register NOT TO Resel Mar 70 Resel . Z 200 bit DC Di Silal Carry C carry -

0 FSR 0 JADT 0 24 PELMIN 8 12 mayeam Co 16 12 Fight Level SLack in sed registers According 17 CPU set. instruction instruction Specific OF execulia 90 made must be understood 6 can South beroie register these of USE contain the C OV regeter status crevands ave 8 bits Luso when carry bit a q bit result OCCUL Can Logether , added = H a; -A 1000 00 B = 11 9 1000 00 1 B 11 22 001000 10 1 For CB. 10001 100 B 10001 100 B

100 00 000 - B 100010001 = B 01100111 Add this minuend ther And 1001000 1 011 0111 B 000000 comy but signal that carry from B tower 4 bit occur durs 8 bit addition. 0011 1000 F 000 1.5 0 0 B 000111 0000 YESUIL oF cary from bit 3 to bit 4 705: Ebr. This USEF-1 digit (any bit is coded number in which each 8 bit byte contains Luo 4 bit binary coded decimal digits. bet status RPO; Select banko STATUS, RPO; Select Bank 1 Jed the status Bits 7 x 6 of the Family of unused by Pic micro controllers discussed in these topics. For 's the Pointer used TSR induced addressing,

16 C PIC 4:0gram OF BIOCK ≤][= J]]¤] ∃ 5 portod PORTC 33 b NEL Ę C InterFoo CCFR2L 9 ist of BUE 240 ANT Derthrow CCPR2H 7 4422 THARIN 154V 20% I MIER SERVIN 557 Con BIC 800 HOUL N12215 ちいかいれ 210 ALF 2152 Jonat of 725 pi d 103 125 103.10 3 3180-3 PORTON PORT ×13 NU WACKED COO TOTOM MULLICK ST DOL NNN0

- HIGH Performance RISC (PU single word instruction 35 DONY operating speed DC- 20 mHz Clock DC . 200M - Interopt capability Eight lever deep handware stack Direct, Induct relative address modes projean code protection Power Saving Sleep made oscillator optio selectable FUILY Static design sink/ source - coment 1-ligh cons 1000 ADDEN LIMA @ SV, ISWA Expical Lypical Stand by conent LIMA Peripheral Features:-PIC 16 C -1X Time or 8 bit Line/ counter Timer 1 :- 16 bit Liner/counter capture: compare pum module (3) muti channel analog to digit 0 6t

ope begins the interpt where routine. or returns to Senice program. left off line ut having a one . a result 15 JF would subroutin Cair instruction 2109 program memory 1098 454321 Parts 2 775 7211 312 11 10 9. 800 instruction (1150) 70 program counter Bils 10 the 10 Special 10aded 9P 3 Ove. 50 bit. Line program counter Same PEL ATH. ME of the called 6 6.65 12 × 11 regista pograms langer 10aded n GNE Can ber for Lo ensure it is necessory Program than this OY is set 3 PCLATH the bit PO Line a 1) each appropriates C leaved instruction goto The called 15 Subroutin advess Lite 11 dels to total

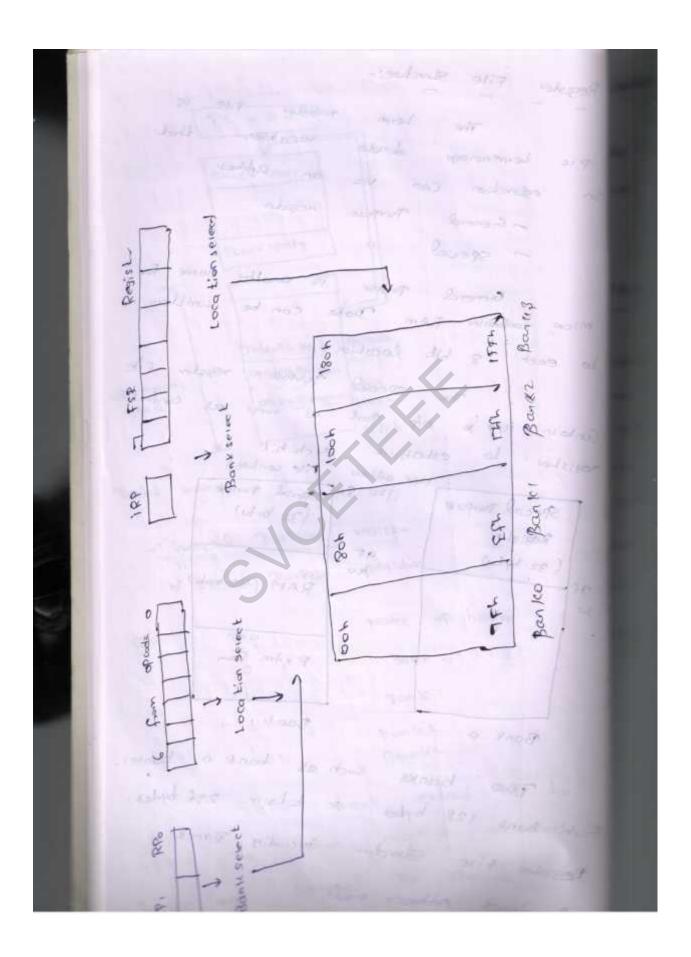

Hilemon organization Data program memory memory For SFRS For accession brogram 2 Capacity 256 CORPacity 44 × 14 11000 by les 2 Bank Banko Capacity 128 byte Capacity OF CONT 1 a Date SFR Extra Rem RAH memor SFR Program memory organization organization 1924 Data memory × memory organization: program It is capable of addressing program memory space. The reset HICX14 an vector is out - offic and intempt vector is cooth.

PC ~ 12.0> SLOLOK LEVEL SLACK LAIM 8 000 4h ntough week poosh onch' Progen USP+ memory otter ou crub wewo 1000h 590.00 1FEP h memory . bata regist+ eogx1 - General register 9050 Specif W. bank 70 NOME PRO (281 Bank 0 0 0 Bouk 0 0 Banks BOOKS 90 extend bank Fach rocation of LOW The reversed for SPECE

SUCE

Register File Structure:-Lerm register File is terminology denote location that an address 219 Via indunction Can Con Purpose resister - General - special 1. 14 General purpose is another name for micro controller RAM. Data can be written to each 8 bit location registar - File special Phypase . The wer les con bol Contain the port of Port 20 register to establish each bit. File content They address (128) 80 - Recial Purple Special Purpose (32 by-ka) Register 3P (32 byte) A O. RAM (32 by-Li) 20 31/20 Fxtra Ram Banki Bank O Two banks such as bank o, banks, Each bank 128 bytes & totally 236 bytes. Registar File Structure including Direct 1 addressing made

Modes:-Kablessing Helhod of Stecifying detail operated by instruction KUDA to be addressing mode 0.5 a direct Addressing mode 11 ME2/2 + 8 Indirect Addression o mode Addressing Mode: use only Thits instruction Divect 10 identify Register, The Address. of the register file must come from PR. setterate register bank Select the banks of a resister divide in to high depend the FI. H of mode a deversion Lhat instruction on value RPD. Every direct addressing mode. Can employ Induct address mode :-8 bit address is First in to FSR. A special register serve as an address Pointer to any address through out after A subsequent direct address register File. of INDE will a chually access

Addess Duect Service to a 12 10 9 13 11 6 Registe 0 Freist 100 0 0 0 adora 1 4 4.32 763 13 12 10 P 8 RAH Regul 0 0 27 RAM Extre 9 Ra overted Bile File content INDF 0 00 0 0 0 24 14 D 1000

Induction set:-Instruction set For PIC 16CTHX Consist 35 induction. Some of these instruction on by Le oriented. Byte oriented Instructions. Byte oriented instruction that require two parameter except the of to be replace by name special purpose register Bit overted instudion: -Bit oriented instruction also s to be replaced. expect parameter Here purpose register by name of special on PAM Nariable Zear 2 6 LASS STATUS , 2 Likeral Instruction-The literal instruction require an operand having a known value of a label that represent known value many Fox eg Num equation of H, Assign of H to blog, (a constant) a second to refring man & whom - will mave will be wregister Every instruction Fit in a single 14 bit word, every instruction also

Siraio cycle

Mnemonic operands Description cycle state 1.15 clear bit bio bit 9.2 hef set bit b of regula 5.6 bof Concell. clear w CITUS 2 2 Clear F CINE move f toF tow FF(W) MONF Swap nibbles of F Swapf FROM value to 2 1 And interal Culture ¥ .... literal value Inclusive K WIN01 Exclusion K Korlis Exclosive COR) tto) XOTUF bit manipulation Sirgue clear bit o OF PORTB ber PORT B. com hit Set STATUSIC bsf Clean move working resiste CIND - Clear - Clear Lemporary variable CINE . Jempi i load 5 to 19 may lis 5 10 local iD moule is is

Incoment Decrement/ complements incf Temp 1, f :- Increment Temp 1 WZ- Tempiti; Temti unchar inch Templing :- will temp com & Temp1, us -multiple bit manipulation and two B DO 000 III :- for unter 5 bits of us Jempi & Jempi & D and of Templet :-:- WZ TEMPI & W Jemp 1. f :- Temps B' 00000 III': - complement power 3 bits TOLOF + CARD W ROX IPMOR - 200 : -Tempi, 9you use Add/ subtract :-add subtract :-0,17 addust : - Temp 1, f conditional branch:e next instruction Templioir Skip the next besc:-BEFSS :- STATUS C Templet Giorio / Cari There :- laber The goto e a doit of a trund young

Simple operations: the 35 instruction with 004 worth while to explore Some it is instruction. recents source of Commonly Sequence: -Filher or Assume an instruction that affect 2 bit has just been executed. Then one instructed sedan the result depend or con Linwith 00 or arother is to be executed after either case IE CLE SKIP est bit STATUS 2 . bEEsc got z get Instruction to exercise ZCLEad 2:0 goto z do Justanction execule ZSEE ZE 16 i carry on. 2904 16 bit Cour le Decrement 30 byte nord Assume Calle low by be called county & Court L. F: Set z if lower MOVE COUNTLY STATUS Z: JE SO hisa

Test a Bit Variable for zero:-Mov f count L. F .- Set 2 iF lower byte =0 bless sintus, 2 = JF not, Hen done testing MOUF COUNTHIF Set z if Alter by Le =0 goto Both zero :- Branch if 16 bit variable =0 Because of pipering to because the chip Can Execute Five Lycle every micro second. 1.6 These sequences are executed wickly For ea 16 bit decrement seduence reasix four cycle there fore Laker only 0.8 hrs. (whether or not branch is tarken) 1 Martine to execute 2. Because the Instruction set can operate directly on RAM Variable, many operations avoid the overhead associated with other microcombolie where in operand in memory encody be first Loaded in to an accumulation restored to memory. 11.77 Hen operate on res