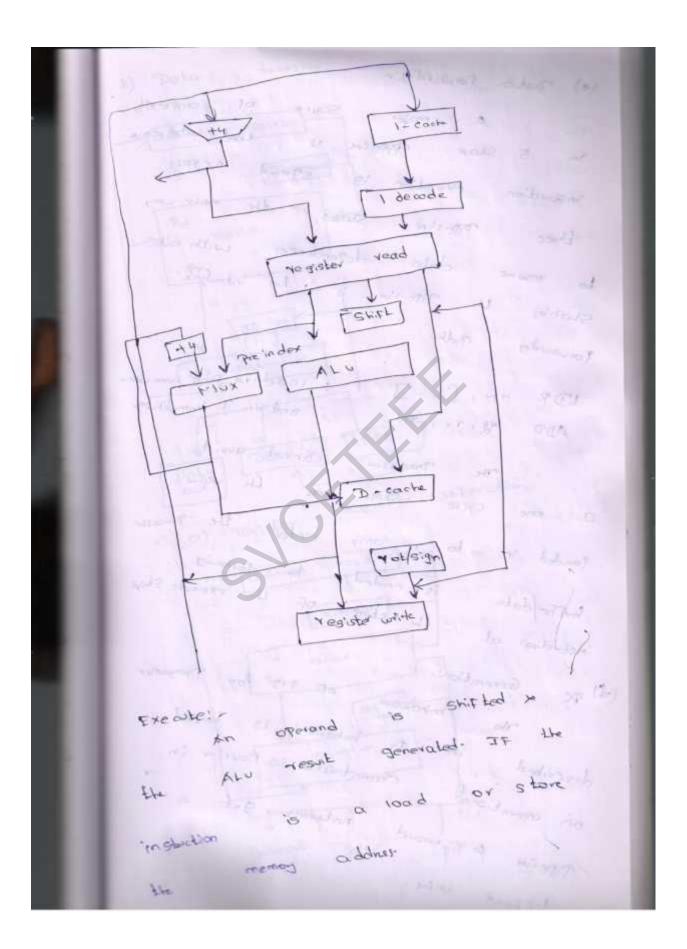

Unit-5 ARM organization :-And organization LING STig 3 stage ARM organization of an The Piperine with a 3stage vegister. address Incrementer Pa YEGISLW 2 module Voca addie Level 30 proit tonk oare) shifter ALU Laka in resist. olata out resistar bank which Slove register state 32 has 2 rea The all strate Can GA Port which CERSO the any resist to one write 1. 1. 1. 1. Ports Shifta which Can to access Used o'Pera barel or rotate ONL the 2-35

of the ALU which Perform the anithmetic by the instruction logic Findion reasired \* The address register and incrementer which select and hold all memory address generate securial address when required decoder and associated - The instruction control logic. In a single - cycle data process instruction, two register operands are ereased the value on shift & combined with value on A bus is Alue then vesult is written the back in "Pipe line!" processor up to FIRM 3 stoge pipeline. 3 stoge employ a \* Fetcher instruction is Fetched The instruction the instruction 10 placed memory Witthest Som Correction in the local division of the loca The instruction is decoded , rpipe line \* Deade: and data path control signal Prepared For the next cycle stare own'

execute Felch decode Fetch decide 2. Execule STYPE S Felch execute decale 3. Instantion > Lime instruction is executed multi cycle a when resular less Flow is the erecte decode Felch, NOD Care, add datarta deade Felch STR decode evente Felch ADD execute decode Felch ADD 7 time instrict ion G. Seduena Shouss 76:5 in studior Simple cycle ADD ocard after Strist ADD 20 that access main memory STR , stading can cycles 1.844 the with Shour 25 CONE. memory that Seen 30 even cycle used

All instruction occupy the data path For one of more adjacent cycle 7 toi each cycle that an instruction occepy the data rath. it occupy the decade logic in immediate precedig

-> Branch instruction Frush & refin

AC Behaviour:-OF pipe lined Conseduente ore RAM executed model used 00 counter, which is is that program Visible to user rist must run ahead No.1 OF CURIENT INSTRUCTION

is indeed what happen Same man and the programmer who attempts to de directly through ris must take. account

Summedictable and it should be avoided. and and

especially since later donot have same behaviour in tese cases. 12.53

(Deresta)

5 BTAGE PIPEIIN ARM Overantion.

T prop ? N'inst x chi

dot also all accord of the white the (a) Memory Bottle neck!with reducing Findamental Problem Core stage a 3 the CPI relative La von weilman to data is related to you wednow to data memory will have its performance limit by the available memory band with A 3 by the available State PRM are access memory on every As the result of the above ssues, the higher parformance ARTY CLOCIE CYCLE . 155-031 employee or 5 state data memory selecte instruction COVES have 5 stage The line : (b) The from memory ion Felch Telch in store -the openal rgister decoded to Devolein 15 Instruction shift and Lk Execute: is operand is result generated JF. An uist is load of store ALCA \* address is compteed "instruction nemon

(e) Data Forwardigin source of complexit, trigetine is that because 's speed across Star 5 20 exection instruction ODIA mand States, the piperine with at data dependencies three to introduce to resome Tipe live 25 station Path Torwardin load DR ADD Cannot avoid Trocastor as the volume The SEAN cycle a one the Process enter Formit the execute store by needed BATFA data 70 the start instudion at of 115 by Programes Genera Lion:chaviout (d) pc based behavior is T PC characteristics described on operational c. get naturaly word Piperin alue

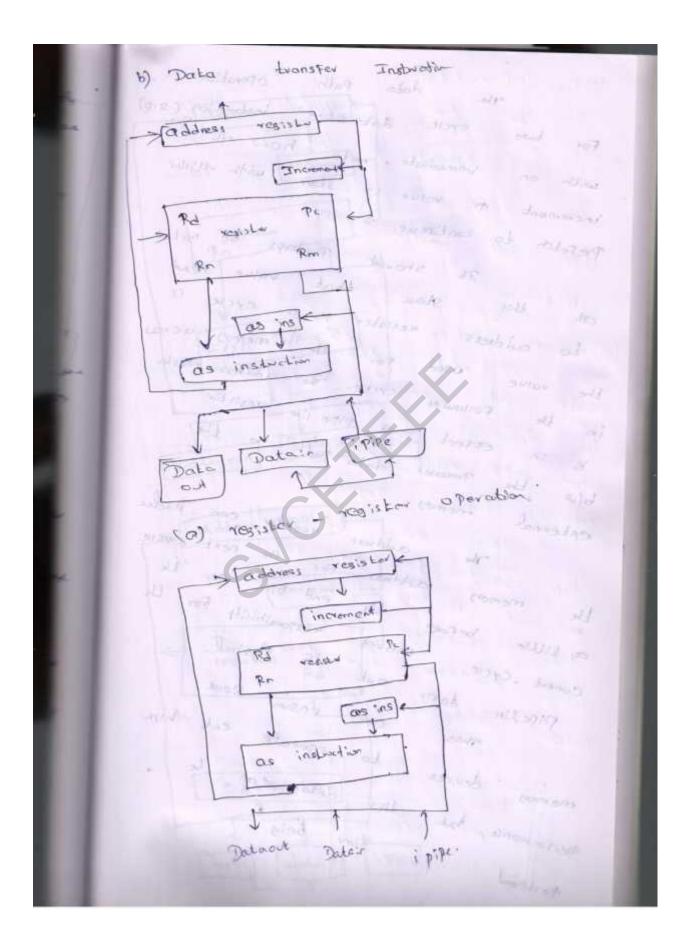

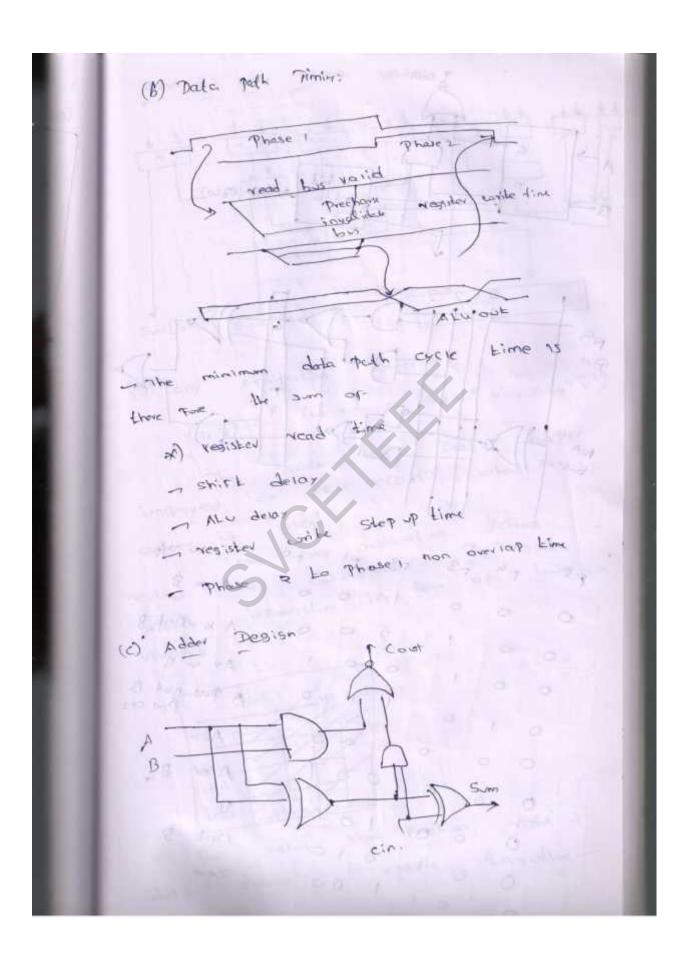

Implementation :-ARIVI Implementation Formaul Arm The that muo approach. to a similar po ch in divided is design the described that is Section path data in Lemalir operate scheme (a) clocking donot ARMS insteal most resister, sensitive edge with 2 phase based 21 design genrate AVE Ph hi clock Clock. 0 ver (07) Signal i/p non allow the use from Merna 117 scheme Det 1 al thes . Nº5 franspevent Pressit - This Cont-olice lover latches 15 move mend alternativy an data Dhase durb opon ave Phase Which open which an Jatches Phese 1 phase 2 I COCH CYCLE

SUCE

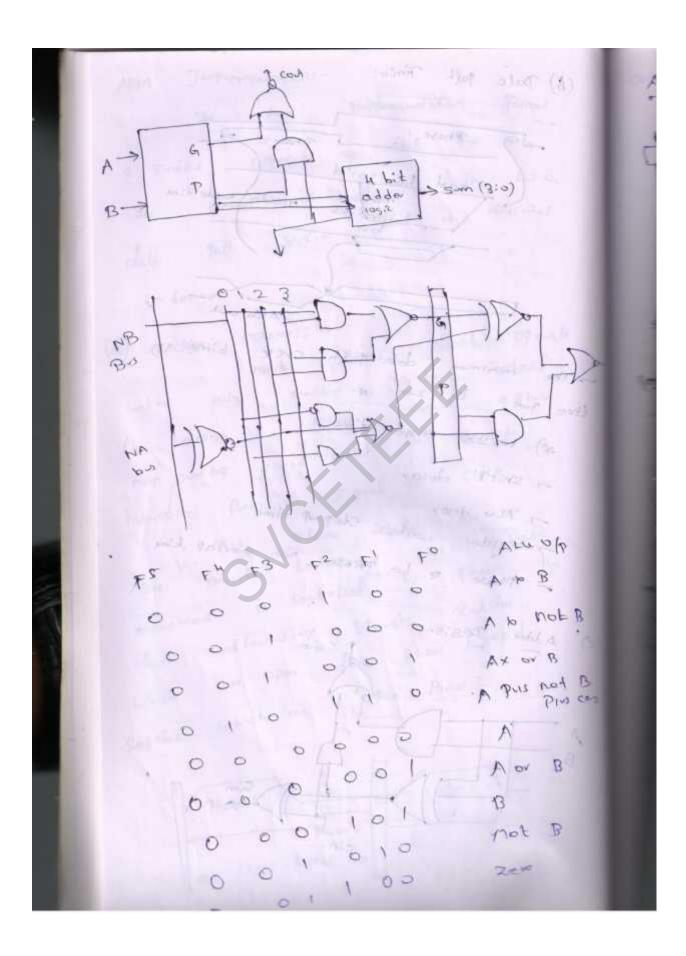

select digger: cony 6 -ARM +1 1-4 1-1-14 ALA 5um [3:0] Ha [ 71:4 ] 50 Adder: bitration (9) carry U. was 10910 adder can where The ENGRO ARH 20 in poured sed Scheme aubitration 15 adder 9030 Carry Conventional reduce information Service VYANIOS C wood 3 rich -142 (3) ida) infi out (4) art (1) and (3) into holer Function right rotate' For 205 is enable Shift diames

Car oul ALW SHIFT mutipisal Carofie Ato SL 72N 0 10 0 D ATB SL #2N A-B LEQN+1) ×2 LOL \$2N A-B ×3 A+B LOLFAN 0 44 LSL EDN+1 A+B 0 XI A-B LSL F2N ×2 Ato +2-LSL \*3 Hundiprises -Speed Ligh mutimination reviorman. where handwoon VC.JOUR "important more embedded 15 Ver Some dedicate of to he. used tean CONT ARIM Sisnal process the System digital Neo Perform Finction control general to 100 B Cir 7 1 1 63 B 1 p. Cat 2 L Cin B Con S Cak B Cin ß ħ. Co BG End Gont LOB 5

SUCE

control studies:. instruction (o grosess KID:HUIM dende control CYCIE PLA com 100d Stor U conto Address Tregista cond-Contr T T uni L This PLA instruction PIFE twetter An Class define 20 uses some internal cycle an operation set-OF 6 data E-res Instre Support ARM Process bytes unsigned unsigned half words , signed to bit signed 2 8 16 bit 2 byte 00 a vigned unsigned wood CINE. these 5'ored are all 32 bit 32 612 instruction aligned. (mar) word 40 must in struction an 20 wood s Thurb 01 Store raust half 2 Stat 400 600

Inabortion 1. WHERE IY instruction multigiz ARH Uniter binary 200 (DP) Pit monthiplais -32 of 90 reart Procl 64 bit Heg, sher a 15 notor birary. 32-bit Binay Froding Rd/RdHi Rn/RdLo P3 1001 Ri Ine S mul 0000 Cond LD BA = (Rm×Ri) twiny (32 bit) KILL 13 000 MLA 001 U.D. SIGN TO St VENULL 100 unspreal UNLAL 1 signed mun 101 Smull 3 110 by. signe Single the Nansfel Frouz Hait since prane Fer There to ARM 619 ward data Sieribie most C 26 bre has , 1000 Lev resil resister that n.eav provided Some Priog to reased menny 14

oft RA Ra Les. CALINE been RId Toil Orel of instruction Form Lond > 2B3 Rd, Rn COFFIC LD SRIST & I condo EB3 ET3 LDRETR byle in vo To share a URFTADO LDR LTPB 000000 ART ADD data byte (.00 Flaif no-1 Inghow instruction ave These o Cessy ARM lete eary Some 90 resit 54 As a orchi the 10 horne LSHOE Some "inst-redion 5 pec 20

con TRO OFFIL 5/11/2 3/L ø e t Cord source destind -:05 Base 10nd/ster 605 Upla 2 Rot 'nder 220) 20.3 Rm 0.00 0 YZ-5,324 instruction ave unsigned hyte ese and word 10.75 Previous to the Simila described OFFSEL is imme d'ate form scaled here and 15:44 6 Section aunitele eight loner to no is Se registe Data Signed Linsie  $^{\circ}$ Signel

Corprocessor Instruction: The ARM architecture Support general mechanism for extend the addition of instruction set through the Corprocessor. The most common use of a coprocessor is the system coprocessor and to comboi to chip Function such as manosement unit on 20 A FLOATED POINT RAM ARM to memory of ache has been develop. AR 11720 Coprocessor resisters their 60 mocessi Arm coprocessor a) sels instruction. register Private responsibility minior that has sole Co proces the or 90 date Concerned with Sul are fransfinstruction and data (b) 60 processor Data o povotion:-Tracesi data operation ave compietes internal se to connection 8 Coprocessstate Couse a resister

this word & signed byte date 12451~ instructions are not support These Processor As a result Some e any AR MI late addition to the architectu 64 OF what shoe homedin to they are some by the duction space as indicated instuction immediate Field. The addressing modes avail with Sprit instruction are a subset CHOIC unsigned the with a vailable 1 Rd 1 arriel IRA cond/o a soury/destination base 100 d Slove imm (310) write/back. Fre/Post index 22 1.1 22 0000 0

Description: -These instruction are very similar to word & unsigned byte formy described in Previow Section 5 H Data Lyte 1 O signed byte 1 Unsigned harf word fighed half word. Multiple Register TransFer instructions ARM MULEPUE brans For ingluction allow any subject vest ter ul 5 Cond 100 P U - load/stor write back restore PSR Up/down Pre/post index Description :-The register list in bottom 16 bit cr induction include a bit For each visible resister, with bit a control Whether or not to is transfor & so on bit is which contril branch of

shap memory & Register Instruction Gien Shap instruction Combine a or an unsigned byte load to F a word in a single instruction. Mormally the two transfer are combined in to atomic memory. Operation cannot be split by an external memory access to there fue used as basis He instruction Can be mechanism. Semaphore 01-Rr Rd 00001001 Rn 00 Cond 0000 B SUM YCHUL destination results base regist unsigned liter used as any should not be RC Base resister Should not be same OF resister as either source or destination (R1) when it is unnecessary to Save or modify Contend OF CPSR of anew made

General Resistan to status Resister The operand which may be register or rotate 3 bit immediate as some way of immediate Form OF operand 2. in dates process instruct. MAR SECOND >3 CRSR\_ FISPER # 232 GE> WISR Scond > 3 CPSP\_ KFed > ISPIR < Fierb Field 111 10/ 0 Cond 0 0 SPSR/CPSR A not/8 bit immediate algame > 10000000) Rm write amplitud