STUCOR APP

Reg

B.E./B.Tech. DEGREE EXAMINATIONS, APRIL/MAY 2019.

(Common-to Electronics and Instrumentation Engineering/Instrumentation and Control Engineering)

Time : Three hours

- Convert  $(101.01)_2$  to decimal number. 1.

- 2.

- 3.

- Find the result of A + A'D + AC'. 4.

- Write down the characteristic table of JK flip-flop. 5.

- What is FSM? List its two basic types. 6.

- Define metastable state 7.

- Draw the structure of PAL. 8.

- State the purpose of test bench. 9. .

- 11. (a) (i)

- (ii)

|         |    |  |    | 14/05 |

|---------|----|--|----|-------|

| . No. : | 11 |  | TT |       |

# Question Paper Code : 80126

Third Semester

**Electrical and Electronics Engineering**

EE 8351 — DIGITAL LOGIC CIRCUITS

(Regulation 2017)

Maximum : 100 marks

Answer ALL questions. PART A —  $(10 \times 2 = 20 \text{ marks})$

Give each one example for error detecting code and error correcting code.

Determine the exact number of half adders and full adders required for performing the addition of two binary numbers of 5-bits length each.

10. Write a VHDL program for an EX-NOR gate using behavioural coding.

PART B —  $(5 \times 13 = 65 \text{ marks})$

Design a 3-input NAND gate circuit using TTL logic. (7)Explain in detail, the generation of Hamming code for 4-bit data. (6)

|      | (b)  | (i)   | Design a 2 input NOR gate using CMOS logic.                                                                                                                                                              | (7)               |

|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|      |      | (ii)  | Explain the operation of RTL inverter circuit with relevand diagrams.                                                                                                                                    | ant<br>(6)        |

| 12,  | (a)  | (i)   | Design a $3 \times 8$ decoder using $2 \times 4$ decoders. Draw the truth table.                                                                                                                         | (7)               |

|      |      | (ii)  | Design a full adden singutter to be the                                                                                                                                                                  | (6)               |

|      | (b)  | (i)   | Simplify and implement the logic function $F(A, B, C) = \Sigma(0, 1, 4, 5, 3)$<br>using logic gates.                                                                                                     | 7)<br>(7)         |

|      |      | (ii)  | Design a $4 \times 2$ priority encoder using logic gates.                                                                                                                                                | (6)               |

| 13.  | (a)  | (i)   | Design a 2-bit synchronous sequential down counter.                                                                                                                                                      | (7)               |

|      |      | (ii)  | Franking the manual of a liter to the second                                                                                                                                                             | (6)               |

|      | (b)  | ·(i)  |                                                                                                                                                                                                          | (7)               |

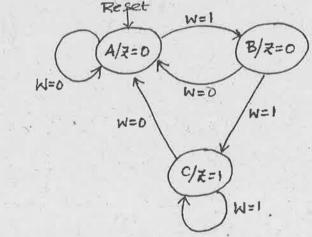

|      |      | (ii)  | Draw the state table for the following state diagram. (                                                                                                                                                  | (6)               |

|      |      | •     | $X = 0 \qquad \begin{array}{c} X = 1 \\ \hline Z = 0 \\ \hline X = 1 \end{array} \qquad \begin{array}{c} X = 1 \\ \hline Z = 1 \\ \end{array} \qquad \begin{array}{c} X = 0 \\ \hline X = 0 \end{array}$ |                   |

| 14.  | (a)  | (i)   | Design a Modulo-6 asynchronous binary up-counter.                                                                                                                                                        | 7)                |

|      | •    | (ii). | Implement the functions $F_1(X, Y, Z) = \Sigma(1, 2, 4, 5)$<br>$F_2(X, Y, Z) = \Sigma(0, 1, 3, 4)$ and $F_3(X, Y, Z) = \Sigma(23, 6, 7)$ using a single PROM order                                       | ;),<br>;le<br>(6) |

| •    | (b)  | (i)   | Differentiate PAL and PLA implementations with the help of the same example $F_2(a,b,c) = \Sigma(0,1,3,4,6,7)$ .                                                                                         | he<br>7)          |

|      | -    | (ii)  | Explain the structure of CPLD with the help of a block diagram. (6                                                                                                                                       | /                 |

| 15., | ·(a) | (i)   | Draw the VLSI design flow chart used for IC design and fabrication (7                                                                                                                                    |                   |

| ŀ    |      | (ii)  | Write down a VHDL code for 8 × 1 Demultiplexer. (6<br>Or                                                                                                                                                 | 6)                |

|      | (b)  | (i)   | Illustrate the two approaches used in VHDL coding with full adde<br>design as your example. (7                                                                                                           |                   |

|      |      | (ii)  | What are components in VHDL? Show step-by-step how a NOI gate component can be created and added in the library. (6                                                                                      | R                 |

2

STUCOR APP

$-(1 \times 15 = 15 \text{ marks})$

equential logic circuit that goes through the 0, 12,14 repeatedly. Use D flip flops for your (15)

$\mathbf{Or}$

ction and implement it using NAND gates only: 1,13,15), with don't care states

(15)

STUCOR APP

Reg. No. :

## **Question Paper Code : 25084**

B.E./B.Tech. DEGREE EXAMINATION, NOVEMBER/DECEMBER 2018.

Electrical and Electronics Engineering

(Common to : Electronics and Instrumentation Engineering/Instrumentation and . Control Engineering)

Time : Three hours

PART A —  $(10 \times 2 = 20 \text{ marks})$

- Draw the DTL based NAND gate. 1.

- 2 complement of the subtrahend (a) 11011 - 11001 (b) 110100 -10101

- Mention the dependency of output in combinational circuits. 3.

- Draw the NAND gate circuit using NOT, AND & OR Gates. 4.

- 5.

- Comment about a preset table counter & ripple counter. 6.

- Draw the block diagram of asynchronous sequential circuit. 7.

- Outline about PLA. 8.

- Draw the basic structure of MOS transistor. 9.

- 10.

Third Semester

EE 8351 — DIGITAL LOGIC CIRCUITS

(Regulations 2017)

Maximum: 100 marks

10/11/2018

EN

Answer ALL questions.

Perform subtraction on the following unsigned binary numbers' using the 2's-

Write the role of master clock generator in synchronous circuits.

List the languages that are combined together to get VHDL language.

(13)

#### PART $\mathbf{\hat{B}}$ — (5 × 13 = 65 marks)

11. (a) Assume a 3-input AND gate with output F and a 3-input OR gate with G output. Show the signals of the outputs F and G as functions of the three inputs ABC. Use all 8 possible combinations of inputs ABC.

#### Or

- (b) Show that a positive logic NAND gate is a negative logic NOR gate and vice versa. (13)

- Given the following Boolean function F = A'C + A'B + AB'C + BC. (13) 12. (a)

- Express it in sum of minterms. (i)

- Find the minimal sum of products expression. (ii)

- Draw the logic diagram of a 2-to-4 line decoder using NOR gates only. **(b)** Include an enable input. (13)

- 13. (a) Explain the operation, state diagram and characteristics of a T flip-flop and master-slave JK flip-flop. (13)

$\mathbf{Or}$

#### Or

- Describe the design procedure with neat diagram about 4 bit (b) bidirectional shift register with parallel load. (13)

- Discuss the operation of SR Latch with NOR and NAND gates analysis. 14. (a)

- Or

- Illustrate about hazards in sequential circuits and the steps to avoid (b) hazards in it. (13)

- 15. (a) Explain the structure and working principles of TTL based Totem-pole output configuration. (13)

#### $\mathbf{Or}$

2

Write a VHDL code to realize a half adder using behavioral modeling and (b) structural modeling. (13)

- 16. (a)

- back to 00, and repeats.

- (b) 5, 6, or 7, the binary output is one less than the input.

25084

STUCOR APP

(13)

#### PART C — $(1 \times 15 = 15 \text{ marks})$

Design a sequential circuit with two D flip-flops A and B, and one input x. When x=0, the state of the circuit remains the same. When x=1, the circuit goes through the state transitions from 00 to 01 to 11 to 10 (15)

$\mathbf{Or}$

Design a combinational circuit with three inputs, x, y and z, and the three outputs, A, B, and C. when the binary input is 0, 1, 2, or 3, the binary output is one greater than the input. When the binary input is 4, (15)

Reg. No. :

B.E./B.T.C.L.DEGREE EXAMINATIONS, NOVEMBER/DECEMBER 2019 Third Semester **Electrical and Electronics Engineering** EE 8351 - DIGITAL LOGIC CIRCUITS Common to : Electronics and Instrumentation Engineering/Instrumentation and **Control Engineering** (Regulations 2017)

Time : Three Hours

Answer ALL questions

PART

- 1. List the different types of output configuration in TTL.

- 2. Given the two binary numbers X = 1010100 and Y = 1000011, perform subtraction (a) X - Y and (b) Y - X using 2's-complements.

- 3. Write the difference between sequential and combinational circuits.

- 4. Draw basic configuration of three PLDs.

- 5. Mention the role of master clock generator in synchronous circuits.

- 6. Define state assignment.

- 7. Name the three types of hazards.

- 8. Define synchronous sequential circuit.

- 9. Mention the languages that are combined together to get VHDL language.

- 10. Expand the T'Base and T'Low predefined attributes.

# Question Paper Code : 90194

Maximum : 100 Marks

(10×2=20 Marks)

(18)

| 90194  | - <b>2</b> -                                                                                                                 |                     |

|--------|------------------------------------------------------------------------------------------------------------------------------|---------------------|

|        | PART – B                                                                                                                     | (5×18=65 Marks)     |

| 11. a) | Explain the two types of MOS families.<br>(OR)                                                                               | (18)                |

| b)     | With the neat circuit diagram, explain the operation of ECL.                                                                 | (18)                |

| 12. a) | Simplify the following expressions in (1) sum of products and of sums<br>a) $x'z' + y'z' + yz' + xy$                         | (2) products<br>(4) |

|        | b) $AC' + B'D + A'CD + ABCD$                                                                                                 | (4)                 |

|        | c) $(A' + B' + D') (A + B' + C') (A' + B + D') (B + C' + D')$                                                                | (5)                 |

|        | (OR)                                                                                                                         | . *                 |

| b)     | Design a half subtractor circuit with inputs x and y and out<br>The givenit subtracts the bits x x and places the difference | • • • • •           |

- The circuit subtracts the bits x-y and places the difference in D and the borrow in B. (13)

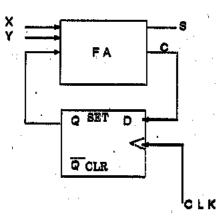

- 13. a) A sequential circuit has one flip-flop Q, two inputs x and y and one output S. It consists of a full-adder circuit connected to a D flip-flop, as shown in figure. Derive the state table and state diagram of the sequential circuit. (18)

#### (OR)

- b) Draw and explain the operation of a JK and master slave JK flip flop. (18) 14. a) Discuss about the hazards in asynchronous sequential circuits and the methods to eliminate them. (18) (OR)

- b) Describe the effect of races in asynchronous sequential circuit design.

###

-8-

15. a) Develop a VHDL code to realize a 3 bit Gray code counter using case statement.

### (OR)

b) Discuss briefly the operators and packages in VHDL.

### PART - C

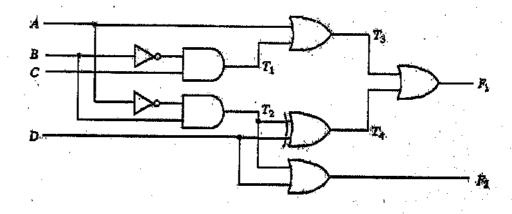

- 16. a) Consider the combinational circuit shown in Fig.

- F, and F, as a function of the four inputs.

- and F, in the table.

- obtained in part (a).

and  $F_{3}$  (A, B, C) =  $\Sigma m(0, 2, 4, 7)$ .

### 90194

(18)

(18)

(15)

(1×15=15 Marks)

i) Derive the Boolean expressions for  $T_1$  through  $T_4$ . Evaluate the outputs of

ii) List the truth table with 16 binary combinations of the four inputs variables. Then list the binary values for T, through  $T_4$  and outputs  $F_1$

iii) Plot the output Boolean functions obtained in part (b) on maps and show that the simplified Boolean expressions are equivalent to the ones

b) Implement the following function using PLA and PAL:  $F_{1}$  (A,B,C) =  $\Sigma m(3,5,6,7)$ (15)

|      | Reg. No.                                                                                              |

|------|-------------------------------------------------------------------------------------------------------|

|      | Question Paper Code : 57308                                                                           |

|      | B.E./B.Tech. DEGREE EXAMINATION, MAY/JUNE 2016                                                        |

| 1    | Third Semester                                                                                        |

|      | Electrical and Electronics Engineering                                                                |

|      | EE 6301 - DIGITAL LOGIC CIRCUITS                                                                      |

| ((   | Common to Electronics and Instrumentation Engineering and Instrumentation and<br>Control Engineering) |

|      | (Regulation 2013)                                                                                     |

| Time | e : Three Hours Maximum : 100 Mari                                                                    |

|      | Answer ALL questions.                                                                                 |

| ta"  | $PART - A (10 \times 2 = 20 \text{ Marks})$                                                           |

| 1.   | Convert the following binary code into a Gray Code :                                                  |

| 184  | 10101110002                                                                                           |

| 2.   | Define fan-in and fan-out.                                                                            |

| 3.   | Write the POS representation of the following SOP function :                                          |

|      | $f(x, y, z) = \sum m(0, 1, 3, 5, 7)$                                                                  |

| 4.   | Design a half subtractor.                                                                             |

| 5.   | Give the characteristic equation and characteristic table of SR flip-flop.                            |

| 6,   | State any two differences between Moore and Mealy state machines.                                     |

| 7.   | What are the two types of asynchronous sequential circuits ?                                          |

| 8.   | State the difference between PROM, PLA and PAL.                                                       |

|      | What is data flow modelling in VHDL ? Give its basic mechanism.                                       |

| 9.   |                                                                                                       |

|      |      |      | PART - B (5 × 16 = 80 Marks)                                                                                                                      |            |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 11.  | (a)  | (i)  | Convert 10101110111011002 into its octal, decimal and hexadecimal                                                                                 |            |

|      |      |      | equivalent.                                                                                                                                       | (6)        |

|      |      | (ii) | Deduce the odd parity hamming code for the data : 1010.                                                                                           | (0)        |

|      |      |      | Introduce an error in the LSB of the hamming code and deduce the steps                                                                            |            |

|      |      |      | to detect the error.                                                                                                                              | (10)       |

|      | (b)  | (i)  | With circuit schematic explain the operation of a two input TTL NAND                                                                              |            |

|      |      |      | gate.                                                                                                                                             | (8)        |

|      |      | (ii) | With circuit schematic and explain the operation and characteristics of a                                                                         |            |

|      |      |      | ECL gate.                                                                                                                                         | (8)        |

| 12.  | (a)  | (i)  | Simplify the following function using Karnaugh Map.                                                                                               |            |

|      |      |      | $f(w, x, y, z) = \sum m(0, 1, 3, 9, 10, 12, 13, 14) + \sum d(2, 5, 6, 11)$                                                                        | (8)        |

|      |      | (ii) | Implement the following function using only NAND gates :<br>$f(x,y,z) = \sum (0, 2, 4, 4)$                                                        | 1          |

|      |      |      | $f(x, y, z) = \sum m(0, 2, 4, 6)$ OR                                                                                                              | (8)        |

|      | (b)  | (i)  | Design a BCD to Excess-3 code converter.                                                                                                          | (8)        |

|      |      | (ii) | Design a full adder and implement it using suitable multiplexer.                                                                                  | (8)        |

| 13   | (a)  | (i)  | Explain the operation of a JK master slave flip flop.                                                                                             | (8)        |

| 1.0. | (4)  | (ii) | Design a MOD-5 counter using T Flip Flops.                                                                                                        | (0)        |

|      |      |      | OR                                                                                                                                                | (0)        |

|      | (b)  | (i)  | Design a serial adder using Mealy state model.                                                                                                    | (8)        |

|      |      | (ii) | Explain the state minimization using partitioning procedure with a suitable example.                                                              | (8)        |

|      |      | ~    |                                                                                                                                                   |            |

| 14.  | (a)  | (i)  | What are Static-0 and Static-1 hazards ? Explain the removal of hazards using hazard covers in K-map.                                             | (9)        |

|      |      | (ii) | Explain cycles and races in asynchronous sequential circuits.                                                                                     | (8)<br>(8) |

|      |      |      | OR                                                                                                                                                |            |

|      | (b)  | (i)  | What are transition table and flow table ? Give suitable examples.                                                                                | (6)        |

|      |      | (ii) | Implement the following function using PLA and PAL :<br>$f(x, y, z) = \sum m (0, 1, 3, 5, 7)$                                                     | (10)       |

|      |      | 1000 |                                                                                                                                                   |            |

| 15.  | (a)  | (i)  | Explain the various operators supported by VHDL.                                                                                                  | (8)        |

|      |      | (ii) | Write the VHDL code to realize a decade counter with behavioural modelling.                                                                       | (8)        |

|      |      |      | OR                                                                                                                                                | (0)        |

|      | ·(b) |      | Explain functions and subprograms with suitable examples.                                                                                         | (6)        |

|      |      | (ii) | Write the VHDL code to realize a 4-bit parallel binary adder with<br>structural modelling and write the test bench to verify its functionality. ( | 10)        |

|      |      |      | and child into coning and write the test bench to verify its functionality.                                                                       | 10)        |

|      |      |      | a second second and an array to the second second second second                                                                                   |            |

|      |      |      | and an                                                                                                        |            |

|      |      | -    | 2 573                                                                                                                                             | 80         |

|      |      |      |                                                                                                                                                   | 00         |

|      |      |      | 영영법 선명도 아랍지? 많은 것 것 모님이 많을                                                                                                                        |            |

| 1    |      |      |                                                                                                                                                   |            |

|      | Reg. No. :                                                     |

|------|----------------------------------------------------------------|

|      | Question Paper Co                                              |

|      | B.E./B.Tech. DEGREE EXAMINATI                                  |

|      | Third Semeste                                                  |

|      | Electrical and Electronics                                     |

| 12.0 | EE 6301 DIGITAL LOG                                            |

| (Çe  | ommon to Electronics and Instrumentation I<br>Control Engineer |

|      | (Regulations 20                                                |

| Time | e : Three hours                                                |

|      | Answer ALL ques                                                |

|      | PART A — $(10 \times 2 = 2)$                                   |

| · 1. | Reduce $a(b+bc')+ab'$ .                                        |

| 2.   | Convert 143 <sub>10</sub> into its binary and binary co        |

| 3.   | Write the POS form of the SOP expressi                         |

| 4.   | Design a Half Subtractor.                                      |

| 5.   | Give the characteristic equation and chara                     |

| 6.   | State the differences between Moore and I                      |

| 7.   | What is a flow table? Give example.                            |

| 8.   | State the difference between PROM, PAL                         |

| 9.   | Give the syntax for package declaration a                      |

| 10   | Write the VHDL code for a $2 \times 1$ multiple                |

# STUCOR APP

# de: 71764 18/05/17 AN

YON, APRIL/MAY 2017.

ter

s Engineering

GIC CIRCUITS

Engineering, Instrumentation and ering)

013)

Maximum : 100 marks

stions.

20 marks)

coded decimal equivalent.

ion f(x, y, z) = x'yz + xyz' + xy'z.

racteristic table of a T Flip Flop.

Melay state machines.

and PLA.

and package body in VHDL.

exer using behavioral modeling.

| <ol> <li>(a) (i) Design a odd-parity hamming code generator and detector for 4-bit data and explain their logic.</li> <li>(ii) Convert <i>EACE</i><sub>15</sub> into its binary, octal and decimal equivalent.<br/>Or</li> <li>(b) (i) With circuit schematic explain the working of a two-input TTL NAND gate.</li> <li>(ii) Compare Totem Pole and open collector outputs.</li> <li>(a) (b) Reduce the following minterms using Karnaugh - Map f(w, x, y, z) = ∑m (0, 1, 3, 5, 6, 7, 8, 12, 14) + ∑d(9, 15). (7)</li> <li>(ii) Implement the following function using a suitable multiplexer f(a, b, c) = ∑m (3, 7, 4, 5). (6)</li> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>(a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = 1 Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E 0</li> <li>D R G 1</li> <li>E F C 0</li> <li>F E 0</li> <li>C F E 0</li> <li< th=""><th>data and explain their logic.<br/>(i) Convert <math>FACE_{15}</math> into its binary, octal and decimal equivalent.<br/>Or<br/>(b) (i) With circuit schematic explain the working of a two-input<br/>TTL NAND gate.<br/>(ii) Compare Totem Pole and open collector outputs.<br/>2. (a) (i) Reduce the following minterms using Karnaugh – Map<br/><math>f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15)</math>. (7)<br/>(ii) Implement the following function using a suitable multiplexer<br/><math>f(a, b, c) = \sum m (3, 7, 4, 5)</math>. (6)<br/>Or<br/>(b) (i) Design a <math>3 \times 8</math> decoder and explain its operation as a minterm<br/>generator. (7)<br/>(ii) Design a full adder using only NOR gates. (6)<br/>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br/>(ii) Design a 5-bit ring counter and mention its applications. (6)<br/>Or<br/>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br/>Flops. (7)<br/>(ii) Using partitioning minimization procedure reduce the following<br/>state table: (6)<br/>Present state Next state Output<br/><math>w = 0 \ w = I \ Z</math><br/>A B C 1<br/>B D F 1<br/>C F E 0<br/>D F E 0<br/>D F E 0<br/>D B G 1<br/>E F C 0</th><th></th><th></th><th></th><th>PART B <math>(5 \times 13 = 65 \text{ marks})</math></th></li<></ol> | data and explain their logic.<br>(i) Convert $FACE_{15}$ into its binary, octal and decimal equivalent.<br>Or<br>(b) (i) With circuit schematic explain the working of a two-input<br>TTL NAND gate.<br>(ii) Compare Totem Pole and open collector outputs.<br>2. (a) (i) Reduce the following minterms using Karnaugh – Map<br>$f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15)$ . (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5)$ . (6)<br>Or<br>(b) (i) Design a $3 \times 8$ decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D F E 0<br>D F E 0<br>D B G 1<br>E F C 0                                                                                                                                                                           |     |                          |       | PART B $(5 \times 13 = 65 \text{ marks})$                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Or(b) (i) With circuit schematic explain the working of a two-input<br>TTL NAND gate.(ii) Compare Totem Pole and open collector outputs.(ii) Compare Totem Pole and open collector outputs.(ii) Compare Totem Pole and open collector outputs.(ii) Implement the following minterms using Karnaugh – Map<br>$f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15). (7)$ (ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5). (6)$ (ii) Design a $3 \times 8$ decoder and explain its operation as a minterm<br>generator. (7)(ii) Design a full adder using only NOR gates. (6)(ii) Design a full adder using only NOR gates. (6)(ii) Design a 5-bit ring counter and mention its applications. (7)(ii) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)(ii) Using para 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)(ii) Using para table $\sum Next state$ Output<br>$w = 0 \ w = 1 \ Z$<br>$A \ B \ C \ 1 \ B \ D \ F \ 1 \ C \ F \ E \ 0 \ D \ B \ G \ 1 \ E \ F \ C \ 0 \ F \ E \ D \ 0 \ C \ C \ C \ C \ C \ C \ C \ C \ C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (b)       (i)       With circuit schematic explain the working of a two-input TTL NAND gate.         (ii)       Compare Totem Pole and open collector outputs.         (ii)       Compare Totem Pole and open collector outputs.         (i)       (i)       Reduce the following minterms using Karnaugh - Map $f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15). (7).         (ii)       Implement the following function using a suitable multiplexer f(a, b, c) = \sum m (3, 7, 4, 5). (6)         (ii)       Implement the following function using a suitable multiplexer f(a, b, c) = \sum m (3, 7, 4, 5). (7)         (iii)       Design a 3 \times 8 decoder and explain its operation as a minterm generator. (7)         (iii)       Design a full adder using only NOR gates. (6)         (ii)       Deraw and explain the operation of a Master - Slave JK Flip Flop.(7)         (ii)       Design a 5-bit ring counter and mention its applications. (6)         Or       Or         (b)       (a)       Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)         (b)       (b)       Design a 4-bit state. Next state Output w = 0 \ w = 1 \ Z         A       B       C         B       D       F         B       D       F       I         C       F       E       0         D       F       C  $ | .1. | (a)                      | (i)   |                                                                                                                                               |

| <ul> <li>(b) (i) With circuit schematic explain the working of a two-input TTL NAND gate.</li> <li>(ii) Compare Totem Pole and open collector outputs.</li> <li>(ii) Compare Totem Pole and open collector outputs.</li> <li>(ii) Reduce the following minterms using Karnaugh - Map f(w, x, y, z) = ∑m (0, 1, 3, 5, 6, 7, 8, 12, 14) + ∑d(9, 15). (7)</li> <li>(ii) Implement the following function using a suitable multiplexer f(a, b, c) = ∑m (3, 7, 4, 5). (6)</li> <li>Or</li> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w:=0 w= I Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>(b) (i) With circuit schematic explain the working of a two-input TTL NAND gate.</li> <li>(ii) Compare Totem Pole and open collector outputs.</li> <li>2. (a) (i) Reduce the following minterms using Karnaugh - Map f(w, x, y, z) = ∑m (0, 1, 3, 5, 6, 7, 8, 12, 14) + ∑d(9, 15). (7)</li> <li>(ii) Implement the following function using a suitable multiplexer f(a, b, c) = ∑m (3, 7, 4, 5). (6)</li> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = I Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                  |     | ì                        | (ii)  | Convert $FACE_{16}$ into its binary, octal and decimal equivalent.                                                                            |

| TTL NAND gate.<br>(ii) Compare Totem Pole and open collector outputs.<br>(ii) Compare Totem Pole and open collector outputs.<br>(ii) Reduce the following minterms using Karnaugh - Map<br>$f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15)$ . (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5)$ . (6)<br>Or<br>(b) (i) Design a $3 \times 8$ decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = 1 \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TTL NAND gate.<br>(ii) Compare Totem Pole and open collector outputs.<br>2. (a) (i) Reduce the following minterms using Karnaugh – Map<br>$f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15)$ . (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5)$ . (6)<br>Or<br>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = 1 \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                   | *   |                          |       | Or                                                                                                                                            |

| 12. (a) (i) Reduce the following minterms using Karnaugh – Map<br>$f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15)$ . (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5)$ . (6)<br>Or<br>(b) (i) Design a $3 \times 8$ decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (7)<br>(ii) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <ul> <li>2. (a) (i) Reduce the following minterms using Karnaugh - Map f(w, x, y, z) = ∑m (0, 1, 3, 5, 6, 7, 8, 12, 14) + ∑d(9, 15). (7)</li> <li>(ii) Implement the following function using a suitable multiplexer f(a, b, c) = ∑m (3, 7, 4, 5). (6)</li> <li>Or</li> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = 1 Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |     | (b)                      | (i) . |                                                                                                                                               |

| $f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15).$ (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5).$ (6)<br>Or<br>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15).$ (7)<br>(ii) Implement the following function using a suitable multiplexer<br>$f(a, b, c) = \sum m (3, 7, 4, 5).$ (6)<br>Or<br>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm<br>generator.<br>(7)<br>(ii) Design a full adder using only NOR gates.<br>(6)<br>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop.<br>(7)<br>(ii) Design a 5-bit ring counter and mention its applications.<br>(6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops.<br>(7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table:<br>(6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$ A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                          | (ii)  | Compare Totem Pole and open collector outputs.                                                                                                |

| Or (b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table : (6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Or (b) (i) Design a 3 × 8 decoder and explain its operation as a minterm<br>generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>(a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>(ii) Design a 5-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = I \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12. | (a)                      |       | $f(w, x, y, z) = \sum m (0, 1, 3, 5, 6, 7, 8, 12, 14) + \sum d(9, 15). $ (7)<br>Implement the following function using a suitable multiplexer |

| <ul> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>13. (a) (i) Draw and explain the operation of a Master - Slave JK Flip Flop. (7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = 1 Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>(b) (i) Design a 3 × 8 decoder and explain its operation as a minterm generator. (7)</li> <li>(ii) Design a full adder using only NOR gates. (6)</li> <li>(i) Draw and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = 1 Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                          |       | $f(a,b,c) = \sum m (3,7,4,5). $ (6)                                                                                                           |

| generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table : (6)<br>Present state Next state Output<br>$w = 0 \ w = 1 \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | generator. (7)<br>(ii) Design a full adder using only NOR gates. (6)<br>13. (a) (i) Draw and explain the operation of a Master – Slave JK Flip Flop.(7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>$w = 0 \ w = 1 \ Z$<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 21 <sup>2</sup><br>1,141 |       | Or                                                                                                                                            |

| <ul> <li>(ii) Design a function and explain the operation of a Master - Slave JK Flip Flop.(7)</li> <li>(ii) Design a 5-bit ring counter and mention its applications. (6)</li> <li>Or</li> <li>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip Flops. (7)</li> <li>(ii) Using partitioning minimization procedure reduce the following state table: (6)</li> <li>Present state Next state Output w = 0 w = 1 Z</li> <li>A B C 1</li> <li>B D F 1</li> <li>C F E 0</li> <li>D B G 1</li> <li>E F C 0</li> <li>F E D 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (ii) Design a faith and explain the operation of a Master – Slave JK Flip Flop. (7)<br>(ii) Design a 5-bit ring counter and mention its applications. (6)<br>Or<br>(b) (i) Design a 4-bit parallel-in serial-out shift register using D Flip<br>Flops. (7)<br>(ii) Using partitioning minimization procedure reduce the following<br>state table: (6)<br>Present state Next state Output<br>w = 0 $w = I$ Z<br>A B C 1<br>B D F 1<br>C F E 0<br>D B G 1<br>E F C 0<br>F E D 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14  | (b)                      | (i)   |                                                                                                                                               |