# DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING EE8351 DIGITAL LOGIC CIRCUITS UNIT – I NUMBER SYSTEM AND DIGITAL LOGIC FAMILIES Part – A

1. Determine (377)<sub>10</sub> in octal and Hexa-decimal equivalent.[N/D'14]

(377)10=(179)16

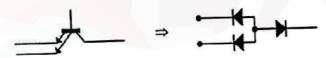

2. Compare the totem – pole output with open collector output. [N/D'14]

| S.No. | Totem pole                                                                            | Open Collector                                                       |

|-------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.    | Output stage consists of pull-up transistor, diode resistor and pull-down transistor. | Output stage consists of only pull-<br>down transistor.              |

| 2.    | External pull-up resistor is not required                                             | External pull-up resistor is required for proper operation of gates. |

| 3.    | Operating speed is high.                                                              | Operating speed is low.                                              |

| 4.    | Output of two gates cannot be tied together.                                          | Output of two gates can be tied together using wired AND technique.  |

- 3. Convert : [A/M'15]

- a) (475.25)<sub>8</sub> to its decimal equivalent. =4x8<sup>2</sup>+7x8<sup>1</sup>+5x8<sup>0</sup>+2x8<sup>-1</sup>+5x8<sup>-2</sup>

- =4x8<sup>2</sup>+7x8<sup>1</sup>+5x8<sup>0</sup>+2x8<sup>-1</sup>+5x8 =256+56+5+0.25+0.078125 =(317.32814)10

- b)  $(549.B4)_{16}$  to its binary equivalent. =5x16<sup>2</sup>+4x16<sup>1</sup>+9x16<sup>0</sup>+11x16<sup>-1</sup>+4x16<sup>-2</sup> =261+64+9+0.6875+0.01562 =(334.703)\_{10}

- 4. Define propagation delay. [A/M'15]

Propagation delay is the average transition delay time for the signal to propagate from

input to output then the signals change in value. It is expressed in ns.

5. What is unit distance code? Give an example. [N/D'15] Unit distance code is a non- weighted code in which next increment or decrement causes the bit transition only at one place. Ex: Gray code. 6. Define Fan-out. [N/D'15]

Fan- Out is defined as the maximum number of inputs of several gates that can be

driven by the output of logic gate maintaining its output levels within the specified

limits.

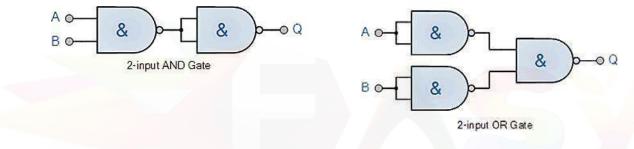

7. Construct OR gate and AND gate using NAND gate. [N/D'16]

- 8. Convert the following Excess-3 numbers into decimal numbers [N/D'16]a) 1011

- b) 1001 0011 0111

- a) Binary equivalent of Excess-3 1011 is →1000 Decimal equivalent of 1000 → (8)<sub>10</sub>

- b) Binary equivalent of Excess-3 1001 0011 0111 is  $\rightarrow$ 0110 0000 0100 Decimal equivalent of 1000  $\rightarrow$  (604)<sub>10</sub>

- 9. Reduce a(b + b'c) + ab' [A/M'17]

$\begin{aligned} a(b+b'c)+ab'&=ab+ab'c+ab'\\ &=a(b+b')+ab'c=a+ab'c \end{aligned}$

10. Convert 143<sub>10</sub> into binary and binary coded decimal equivalent. [A/M'17]

Binary coded decimal equivalent  $\rightarrow$  143<sub>10</sub> is 0001 0100 0011

DIGITAL LOGIC CIRCUITS

#### UNIT – I

# NUMBER SYSTEM AND DIGITAL LOGIC FAMILIES

#### Part – B

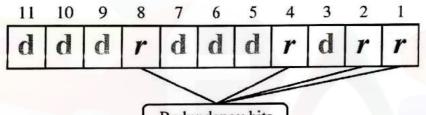

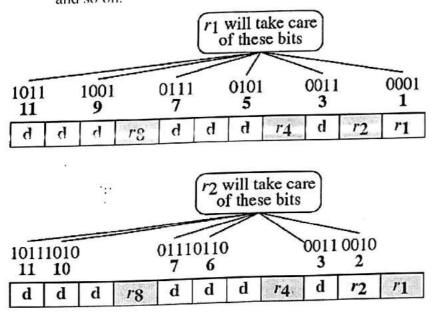

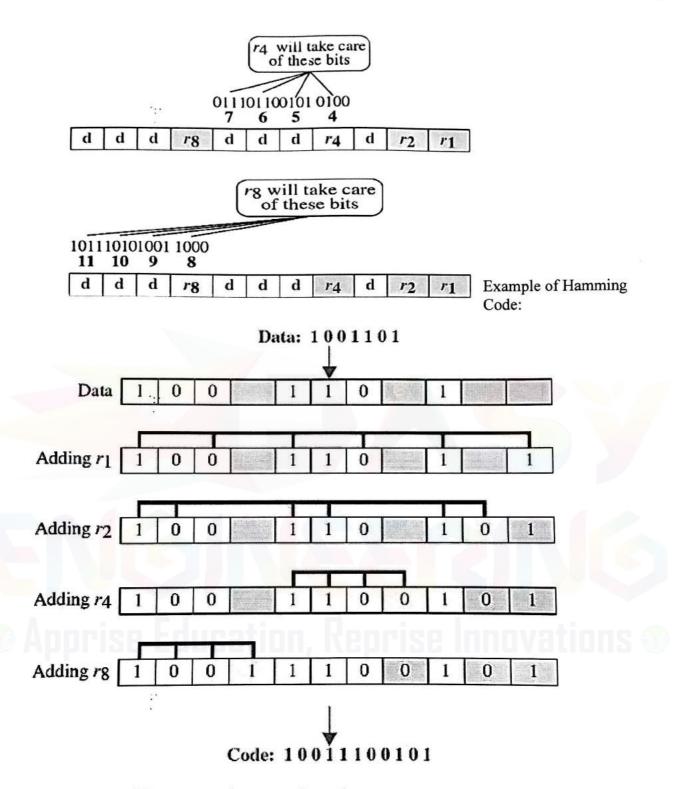

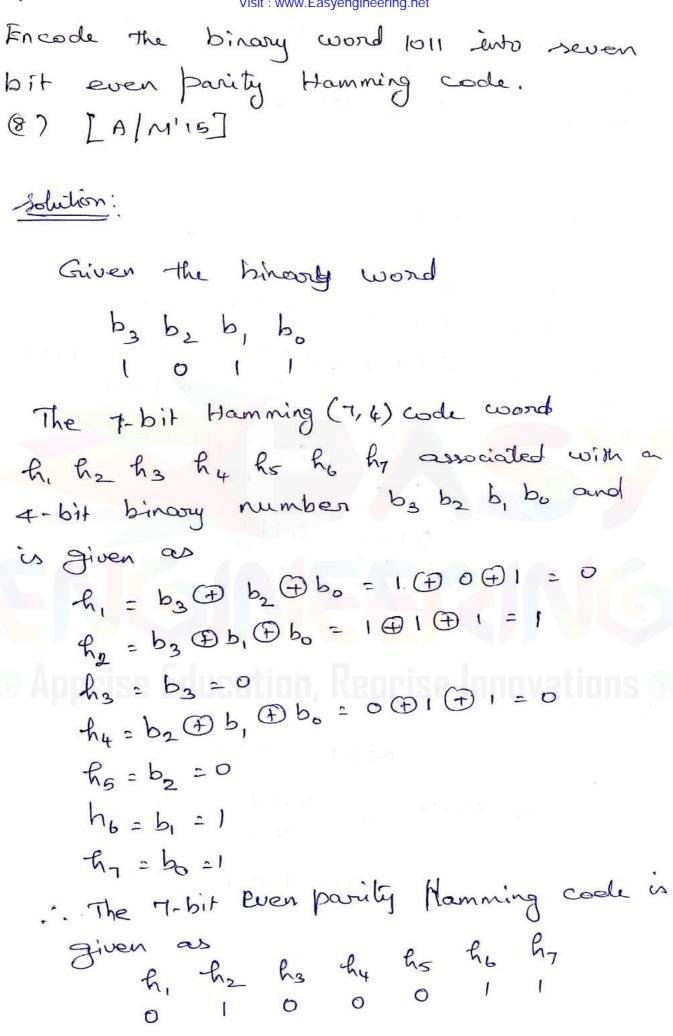

- Explain Hamming code with an example. State its advantages over parity codes. (8) [N/D'14]

- Hamming code is a set of error-correction code s that can be used to detect and correct bit errors that can occur when computer data is moved or stored.

- Hamming codes can detect up to two-bit errors or correct one-bit errors without detection of uncorrected errors.

- Hamming codes are perfect codes for achieving the highest possible rate for codes with their block length and minimum distance called as min Hamming distance.

- A Hamming can be applied to the data unit of any length and uses the relationship between data and redundancy bits.

- For example the seven bit ASCII code requires 4 redundancy bits that can be added to the end of the data or between the original data bits.

Redundancy bits

- In Hamming code, the position of r bits is as follows:

- o  $r_1$  bits 1,3,5,7,9,11

- o  $r_2$  bits 2,3,6,7,10,11

- o  $r_3$  bits 4,5,6,7

- o  $r_4$  bits 8,9,10,11

- > The position of  $r_1$  is chosen for the values which has 1 in the right most position.

- > The position of  $r_1$  is chosen for the values which has 1 in the second last position.

- > The position of  $r_1$  is chosen for the values which has 1 in the third last position.

- > The position of  $r_1$  is chosen for the values which has 1 in the fourth last position and so on.

Advantages of Hamming code over parity codes

- The advantage of Hamming code over a simple parity system that it can correct a single bit error and can also detect 2-bit errors.

- Whereas a parity system with one parity bit can detect single bit errors but cannot correct them.

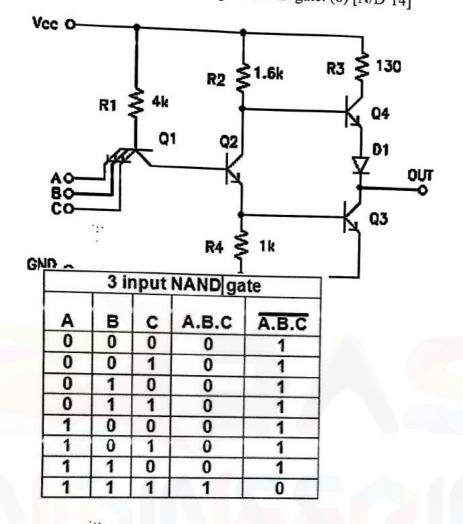

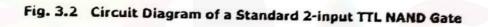

2. Design TTL logic circuit for a 3-input NAND gate. (8) [N/D'14]

- If any input is low, the corresponding base-emitter junction becomes forwardbiased and the transistor conducts.

- The other characteristics of the circuit and its transfer characteristic are identical to those of the inverter circuit.

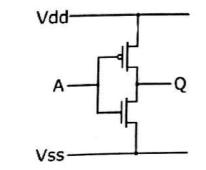

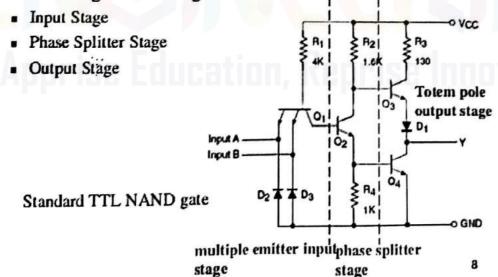

- 3. Draw the MOS logic circuit for NOT gate and explain its operation. (8) [N/D'14]

- When a low voltage (0 V) is applied at the input, the top transistor (P-type) is conducting (switch closed) while the bottom transistor behaves like an open circuit.

- Therefore, the supply voltage (5 V) appears at the output.

- Conversely, when a high voltage (5 V) is applied at the input, the bottom transistor (N-type) is conducting (switch closed) while the top transistor behaves like an open circuit.

- Hence, the output voltage is low (0 V).

- The function of this gate can be summarized by the following table:

| Input         | Output        |

|---------------|---------------|

| High (logic1) | Low (logic 0) |

| Low (logic 0) | High (logic1) |

- The output is the opposite of the input this gate inverts the input.

- One of the transistors will be an open circuit and no current flows from the supply voltage to ground.

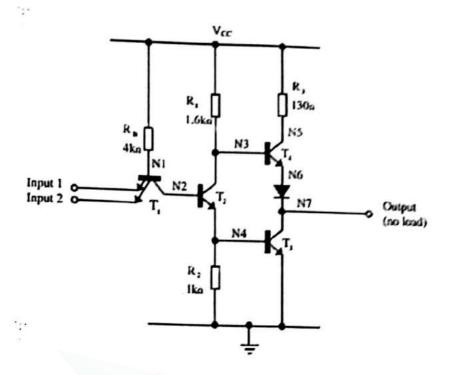

- 4. With circuit schematic, explain the operation of a two input TTL NAND gate with totempole output. (10) [A/M'15]

- 5. With circuit schematic explain the working of a two input TTL NAND gate. (7) [A/M'17]

- The circuit structure is identical to TTL inverter circuit except for the multiple emitter input transistor.

- This is used to implement a diode switching structure in active transistor form using parallel junction diffusions for several emitters.

Fig. 3.1 Multiple Input Emitter Structure of TTL

- If any input is low, the corresponding base-emitter junction becomes forward-biased and the transistor conducts.

- The other characteristics of the circuit and its transfer characteristic are identical to

- those of the inverter circuit.

# Logical Operation

- The direction of conduction of T1 can be in the forward or reverse mode so this should also be noted in the table.

- It can be seen<sup>3</sup> from the table that the output goes LO only when both inputs are HI which verifies the NAND function.

| which veri |     | T  | T   | T <sub>a</sub> | T.  | D   | Output |

|------------|-----|----|-----|----------------|-----|-----|--------|

| IN1        | IN2 |    |     | OFF            | ON  | ON  | HI     |

| LO         | LO  | ON | OFF |                | ON  | ON  | HI     |

| LO         | HI  | ON | OFF | OFF            |     | ON  | HI     |

| HI         | LO  | ON | OFF | OFF            | ON  |     |        |

| HI         | HI  | ON | ON  | ON             | OFF | OFF | LO     |

- 6. Compare totem pole and open collector outputs. (6) [A/M'15]

- 7. Compare Totem pole and open collector outputs. (6) [A/M'17]

# NAND gate with Totem pole output

· : ·

Below is the circuit of a totem-pole NAND gate, which has got three stages

# NAND gate with collector output

| S.No. | Totem pole                                                                                   | Open Collector                                                       |

|-------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1.    | Output stage consists of pull-up<br>transistor, diode resistor and pull-<br>down transistor. | Output stage consists of only pull-down transistor.                  |

| 2.    | External pull-up resistor is not required                                                    | External pull-up resistor is required for proper operation of gates. |

| 3.    | Operating speed is high.                                                                     | Operating speed is low.                                              |

| 4.    | Output of two gates cannot be tied together.                                                 | Output of two gates can be tied together using wired AND technique.  |

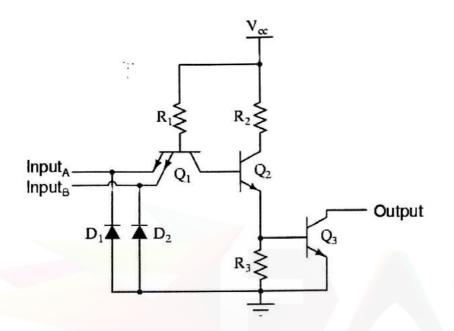

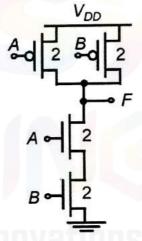

8. Draw the CMOS logic circuit for NOR gate and explain its operation. (8) [N/D'15]

- The circuit has two inputs and one output.

- Whenever at least one of the inputs is high, the corresponding N-type transistor will be closed while the P-type transistor will be open.

- Consequently, the output voltage will be low.

- Conversely, if both inputs are low, then both P-type transistors at the top will be closed circuits and the N-type transistors will be open.

- Hence, the output voltage is high.

- The function of this gate can be summarized by the following table:

| Input (A) 🐺 | Input (B) | Output |

|-------------|-----------|--------|

| Low         | Low       | High   |

| Low         | High      | Low    |

| High        | Low       | Low    |

| High        | High      | Low    |

- If logical 1's are associated with high voltages then the function of this gate is called NOR for negated OR.

- There is never a conducting path from the supply voltage to ground.

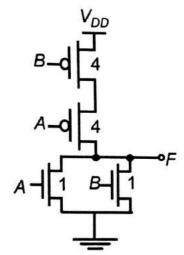

- 9. Explain with an aid of circuit diagram the operation of 2 input CMOS NAND gate and list out its advantages over other logic families. (10) [N/D'16]

- The circuit has two inputs and one output.

- Whenever at least one of the inputs is low, the corresponding P-type transistor will be conducting while the N-type transistor will be closed.

- Consequently, the output voltage will be high.

- Conversely, if both inputs are high, then both P-type transistors at the top will be open circuits and both N-type transistors will be conducting.

- Hence, the output voltage is low.

- The function of this gate can be summarized by the following table:

| Input (A) | Input (B) | Output |

|-----------|-----------|--------|

| Low       | Low       | High   |

| Low       | High      | High   |

| High      | Low       | High   |

| High      | High      | Low    |

- If logical 1's are associated with high voltages then the function of this gate is called NAND for negated AND.

- There is never a conducting path from the supply voltage to ground.

# Advantages of CMOS over other logic families

- a) Low power consumption

- b) High fan out

- c) Temperature stability

- d) Noise immunity

- 10. Briefly discuss weighted Binary code. (4) [N/D'15] Weighted Codes:

- The main characteristic of a weighted code is, each binary bit is assigned by a "weight" and values depend on the position of the binary bit.

- The sum of the weights of these binary bits, whose value is 1 is equal to the decimal digit which they represent.

- In other words, if w1, w2, w3 and w4 are the weights of the binary digits, and x1, x2, x3 and x4 are the corresponding bit values, then the decimal digit N=w4x4 + w3x3+w2x2+w1x1 is represented by the binary sequence x4x3x2x1.

- A sequence of binary bits which represents a decimal digit is called a "code word".

- Thus x4x3x2x1 is a code word of N.

- Example of these codes is: BCD, 8421, 6421, 4221, 5211, 3321 etc.

- Weighted codes are used in:

·:•

- a) Data manipulation during arithmetic operation.

- b) For input/output operations in digital circuits.

- c) To represent the decimal digits in calculators, volt meters etc.

# Apprise Education, Reprise Innovations

| Perform the following and Excess-3 addition<br>(205+569) (8) [1] | addition using BCD                  |

|------------------------------------------------------------------|-------------------------------------|

| Solution :                                                       |                                     |

| BCD Addition                                                     |                                     |

| 569 0101                                                         | 0000 0101<br>0110 1001<br>0110 1110 |

| 774 0111                                                         | 1 0110                              |

|                                                                  | 0110]0100                           |

| 0111                                                             | 0111 0100                           |

| Excess-3 Addition                                                |                                     |

| Excess-3 code of                                                 | 205                                 |

| 0101                                                             | 0011 1000                           |

| Excess-3 code of                                                 | 569<br>V                            |

| 000                                                              | 1001 1100                           |

.

1.

8-bits of data and 4 parity pits is read from memory. what was the original 8-bit data word that have been \_\_\_ A 12-bit Hamming code word containing written into memory ib the 12-bit word (12) [N]D'15] read out is as (1) (01110010100 (2) 11111110100 -Solution : (1) (01110010100 12-bit Hamming code is given as

P., P2, P3 & P4 are pointy bits astile the remaining hits are data-bits. The bit data is 10110011

# UNIT – II COMBINATIONAL CIRCUITS Part – B

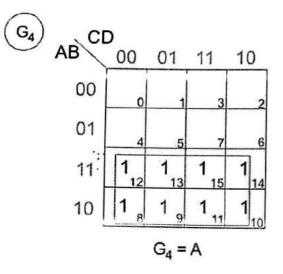

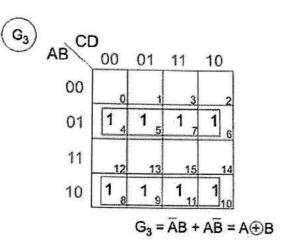

- Design a 4-Bit binary to gray code converter and implement it using logic gates. (8)[N/D'14]

- The logical circuit which converts binary code to equivalent gray code is known as **binary to gray code converter**.

- The gray code is a non weighted code.

....

• The successive gray code differs in one bit position only that means it is a unit distance code. It is also referred as cyclic code. It is not suitable for arithmetic operations. It is the most popular of the unit distance codes. It is also a reflective code.

| Decimal | 4 bit B | inary N | umber |   | 4 Bit C               | Gray cod       | e              |    |

|---------|---------|---------|-------|---|-----------------------|----------------|----------------|----|

| Number  | A       | B       | C     | D | <i>G</i> <sub>1</sub> | G <sub>2</sub> | G <sub>3</sub> | G4 |

| 0       | 0       | 0       | 0     | 0 | 0                     | 0              | 0              | 0  |

| 1       | 0       | 0       | 0     | 1 | 0                     | 0              | 0              | 1  |

| 2       | 0       | 0       | 1     | 0 | 0                     | 0              | 1              | 1  |

| 3       | 0       | 0       | 1     | 1 | 0                     | 0              | 1              | 0  |

| 4 ·     | 0       | 1       | 0     | 0 | 0                     | 1              | 1              | 0  |

| 5       | 0       | 1       | 0     | 1 | 0                     | 1              | 1              | 1  |

| 6       | 0       | 1       | 1     | 0 | 0                     | 1              | 0              | 1  |

| 7       | 0       | 1       | 1     | 1 | 0                     | 1              | 0              | 0  |

| 8       | 1       | 0       | 0     | 0 | 1                     | 1              | 0              | 0  |

| 9       | 1       | 0       | 0     | 1 | 1                     | 1              | 0              | 0  |

| 10      | 1       | 0       | 1     | 0 | 1                     | 1              | 1              | 1  |

| 11      | 1       | 0       | 1     | 1 | 1                     | 1              | 1              | 0  |

| 12      | 1       | 1       | 0     | 0 | 1                     | 0              | 1              | 0  |

| 13      | 1       | 1       | 0     | 1 | 1                     | 0              | 1              | 1  |

| 14      | 1       | 1       | 1     | 0 | 1                     | 0              | 0              | 1  |

| 15      | 1       | 1       | 1     | 1 | 1                     | 0              | 0              | 0  |

That means. in 4 bit gray code, (4-1) or 3 bit code is reflected against the axis drawn after  $(2^{4-1})^{\text{th}}$  or  $8^{\text{th}}$  row.

The bits of 4 bit gray code are considered as G<sub>4</sub>G<sub>3</sub>G<sub>2</sub>G<sub>1</sub>. Now from conversion table,

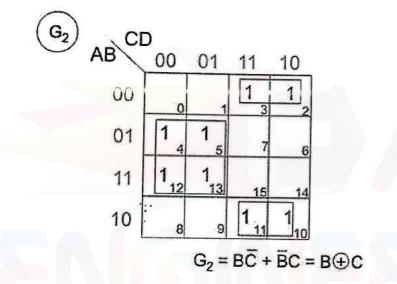

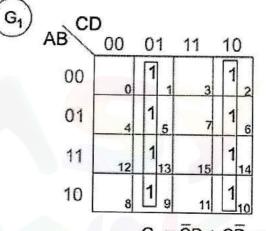

$$G_4 = \sum m(8,9,10,11,12,13,14,15), \ G_3 = \sum m(4,5,6,7,8,9,10,11)$$

$G_2 - \sum m(2,3,4,5,10,11,12,13), \ G_1 = \sum m(1,2,5,6,9,10,13,14)$

# K-map Simplification

$G_1 = \overline{C}D + C\overline{D} = C \oplus D$

Logic Diagram:

Logic Circuit for Binary to Gray Code Converter

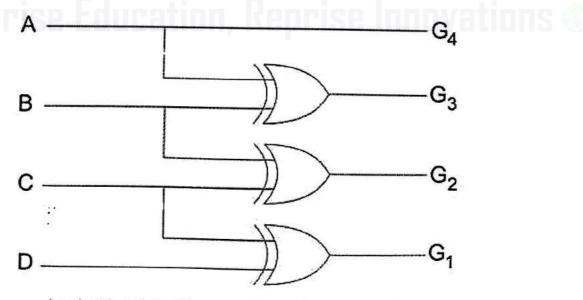

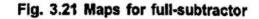

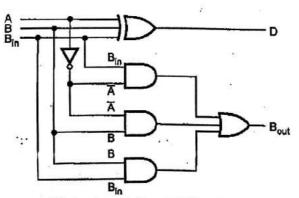

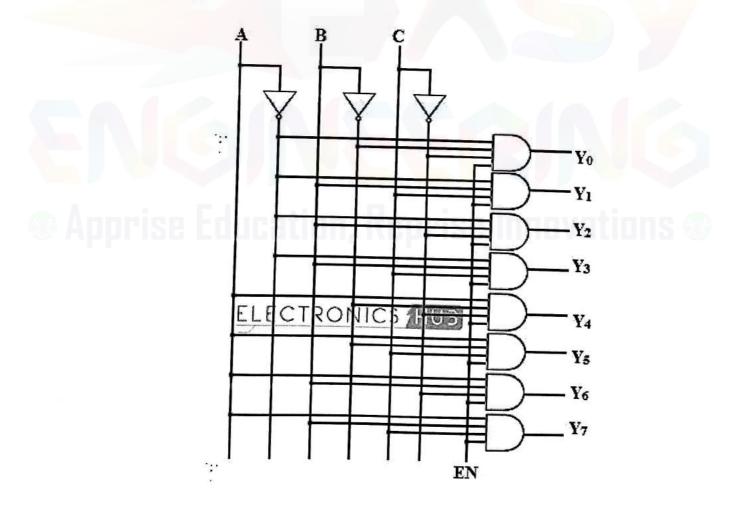

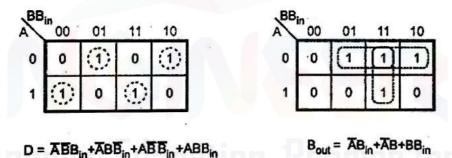

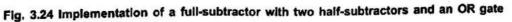

- Design a full subtractor and implement it using logic gates. (8)[N/D'14]

Full Subtractor.

- Full subtractor performs subtraction of two bits, one is minuend and other is subtrahend.

- The input of a full subtractor consists of three bits (A, B and Bin) and two outputs are DIFFERENCE output (D) and BORROW (Bout)

- Full subtractor performs subtraction of two bits, one is minuend and other is subtrahend. In full subtractor '1' is borrowed by the previous adjacent lower minuend bit.

# Truth Table

|   | Inpu | ut  | ( | Output |

|---|------|-----|---|--------|

| Α | В    | Bin | D | Bout   |

| ũ | O    | 0   | 0 | 0      |

| 0 | 0    | 1   | 1 | 1      |

| 0 | 1    | 0   | 1 | 1      |

| 0 | 1    | 1   | 0 |        |

| 1 | 0    | 0   | 1 | 0      |

| 1 | 0    | 1   | 0 | 0      |

| 1 | 1    | 0   | 0 | 0      |

| 1 | 1    | 1   | 1 | 1      |

# K-map Simplification

For B<sub>out</sub>

$D = \overline{ABB}_{in} + \overline{ABB}_{in} + \overline{ABB}_{in} + \overline{ABB}_{in}$

Bout = ABin+AB+BBin

Logic Diagram using logic gates

Fig. 3.23 Implementation of full-subtractor

# Logic Diagram using half subtractors

# Fig. 3.24 Implementation of a full-subtractor with two half-subtractors and an OR gate

3. Design a BCD to Exces-3 code converter. (8) [A/M'15]

# Truth table :

|    |   | B | CD |   | Excess-3 |   |   |   |

|----|---|---|----|---|----------|---|---|---|

|    | A | B | C  | D | W        | X | Y | Ζ |

| 0  | 0 | 0 | 0  | 0 | 0        | 0 | 1 | 1 |

| 1  | 0 | Û | 0  | 1 | 0        | 1 | 0 | 0 |

| 2  | Û | Ú | 1  | Ú | Ú        | 1 | 0 | 1 |

| 3  | 0 | Q | .1 | 1 | 0        | 1 | 1 | 0 |

| 4  | 0 | 1 | Ö  | 0 | 0        | 1 | 1 | 1 |

| 5  | 0 | 1 | 0  | 1 | 1        | 0 | 0 | 0 |

| 6  | 0 | 1 | 1  | 0 | 1        | 0 | 0 | 1 |

| 7  | 0 | 1 | 1  | 1 | 1        | 0 | 1 | 0 |

| 8  | 1 | U | C  | 0 | 1        | 0 | 1 | 1 |

| 9  | 1 | 0 | 0  | 1 | 1        | 1 | 0 | 0 |

| 10 | 1 | Û | 1  | 0 | Х        | Х | Х | Х |

| 11 | 1 | 0 | 1  | 1 | Х        | Х | Х | Х |

| 12 | 1 | 1 | 0  | 0 | Х        | Х | Х | Х |

| 13 | 1 | 1 | 0  | 1 | Х        | Х | Χ | Х |

| 14 | 1 | 1 | 1  | 0 | Х        | Х | Х | Х |

| 15 | 1 | 1 | 1  | 1 | Х        | Х | Х | Х |

·:•

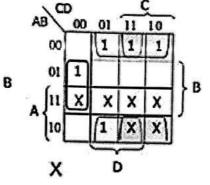

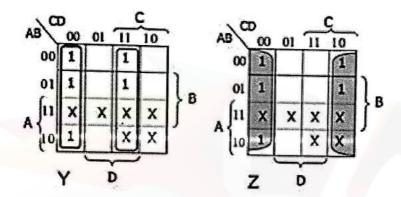

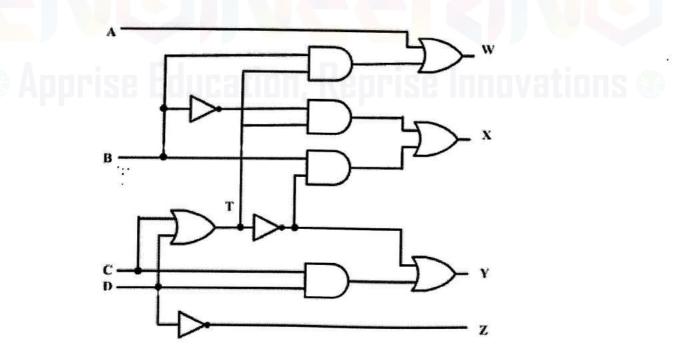

# K-map Simplification

Z = D'

Logic Diagram of BCD to Excess-3 code converter

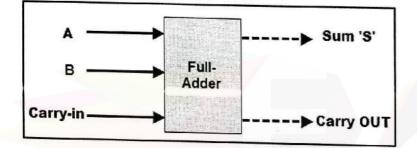

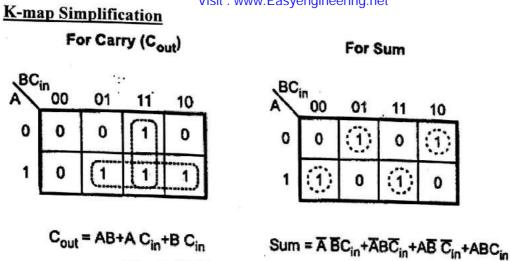

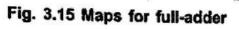

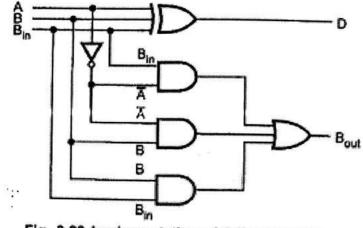

- 4. Design a full adder using two half adders and an OR gate. (8)[A/M'15]

- 5. Design a full adder using only NOR gates. (6) [A/M'17]

- An adder is a digital circuit that performs addition of numbers.

- The half adder adds two binary digits called as augend and addend and produces two outputs as sum and carry; XOR is applied to both inputs to produce sum and AND gate is applied to both inputs to produce carry.

## **Full Adder**

- The full adder adds 3 one bit numbers, where two can be referred to as operands and one can be referred to as bit carried in. And produces 2-bit output, and these can be referred to as output carry and sum.

- The difference between a half-adder and a full-adder is that the full-adder has three inputs and two outputs, whereas half adder has only two inputs and two outputs.

- The first two inputs are A and B and the third input is an input carry as C-IN.

# Full Adder Truth Table:

|   | INPUTS | OUTPUT             |       |   |  |

|---|--------|--------------------|-------|---|--|

| A | В      | C-IN               | C-OUT | S |  |

| 0 | 0      | 0                  | 0     | 0 |  |

| 0 | 0      | 1                  | 0     | 1 |  |

| 0 | 1      | 0                  | 0     | 1 |  |

| 0 | 1      | 5. 60 <b>1</b> 000 | 1     | 0 |  |

| 1 | 0      | 0                  | 0     |   |  |

| 1 | 0      | 1                  | 1     | 0 |  |

| 1 | 1      | . 0                | 1     | 0 |  |

| 1 | 1      | 1                  |       |   |  |

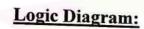

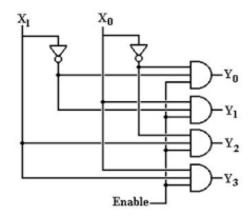

6. Design a 3 x 8 decoder and explain its operation as a minterm generator. (7) [A/M'17]

# Truth table:

| Inputs    |             |            |          |                | Outputs        |                |                |                |                |                |    |  |

|-----------|-------------|------------|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|--|

| EN        | Α           | В          | С        | Y <sub>7</sub> | Y <sub>6</sub> | Y <sub>5</sub> | Y <sub>4</sub> | Y <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Yo |  |

| 0         | ×           | ×          | ×        | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0  |  |

| 1         | 0           | 0          | 0        | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1  |  |

| 1         | 0           | 0          | 1        | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0  |  |

| 1         | 0           | 1          | 0        | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0  |  |

| 1         | 0           | 1          | 1        | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0  |  |

| HAREN SAN | 1           | 0          | 0        | 0              | 0              | 0              | 1              | 0              | 0              | 0              | 0  |  |

| 1         | S.S.VIENNAS | 0          | 1        | 0              | 0              | 1              | 0              | 0              | 0              | 0              | 0  |  |

| 1         | 1           | 1          | 0        | 0              | 1              | 0              | 0              | 0              | 0              | 0              | 0  |  |

| 1         | 1           | arian sana | all face | 22.0902.064    | ō              | 0              | 0              | 0              | 0              | 0              | 0  |  |

# Logic function:

$$Y_0 = A'B'C'$$

$Y_1 = A'B'C$

$Y_2 = A'BC'$

$Y_3 = A'BC$

$Y_4 = AB'C'$

$Y_5 = AB'C$

$Y_6 = ABC'$

$Y_7 = ABC$

Visit : wScanged by Camscanner

- 7. Design a full subtractor and realize using logic gates. (8) [N/D'15]

- Design a full subtractor and realize using logic gates. Also implement the same using half subtractors. (13) [N/D'16]

# Truth Table:

| Inputs |   |                 | Outputs |      |  |

|--------|---|-----------------|---------|------|--|

| A      | В | B <sub>in</sub> | D       | Bout |  |

| 0      | 0 | 0               | 0       | 0    |  |

| 0      | 0 | 1               | 1       | 1    |  |

| 0      | 1 | 0               | 1       | 1    |  |

| 0      | 1 | 1               | 0       | 1    |  |

| 1      | 0 | 0               | 1       | o    |  |

| 1      | 0 | 1               | 0       | 0    |  |

| 1      | 1 | 0               | 0       | 0    |  |

| 1      | 1 | 1               | 1       | 1    |  |

Table 3.9 Truth table for full-subtractor

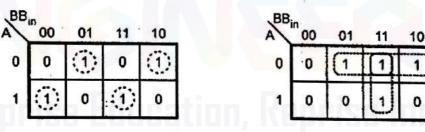

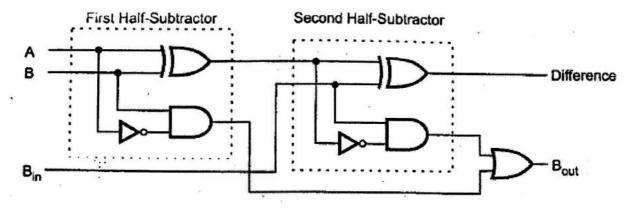

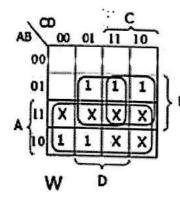

### K-map simplification:

For Bout

Fig. 3.21 Maps for full-subtractor

Full subtractor using two half subtractors

•

# Full subtractor using logic gates

Fig. 3.23 Implementation of full-subtractor

9. Design a full adder using only NOR gates. (6) [A/M'17]

• • •

#### Visit : wScannedobye Clamscanner

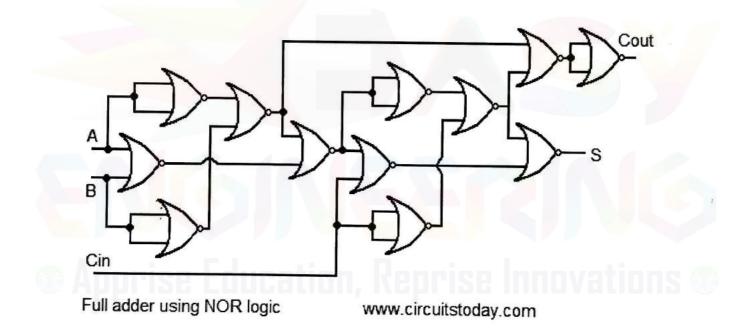

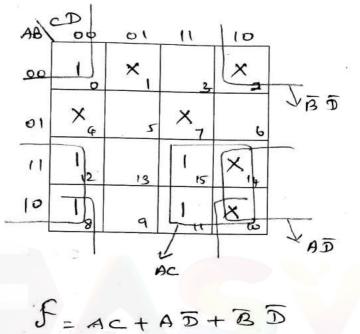

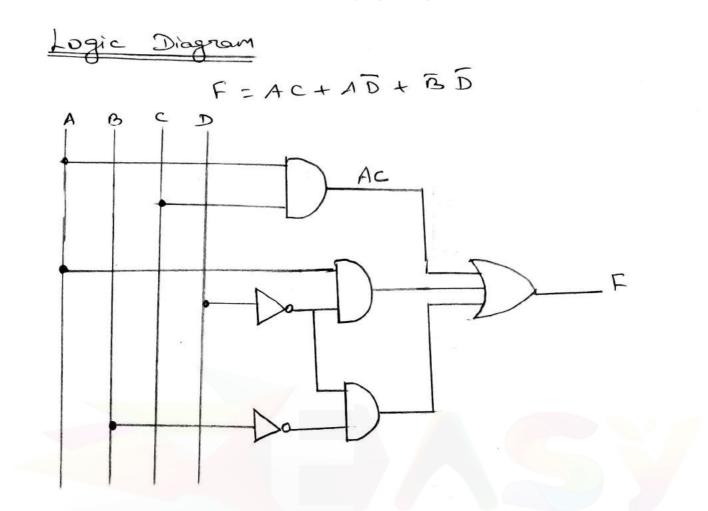

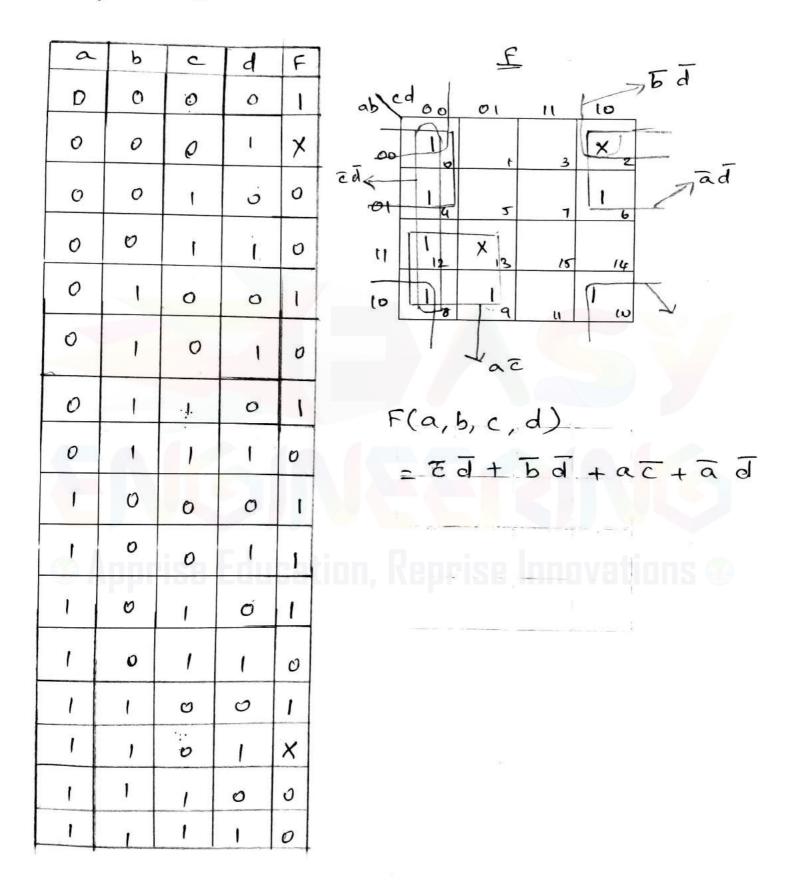

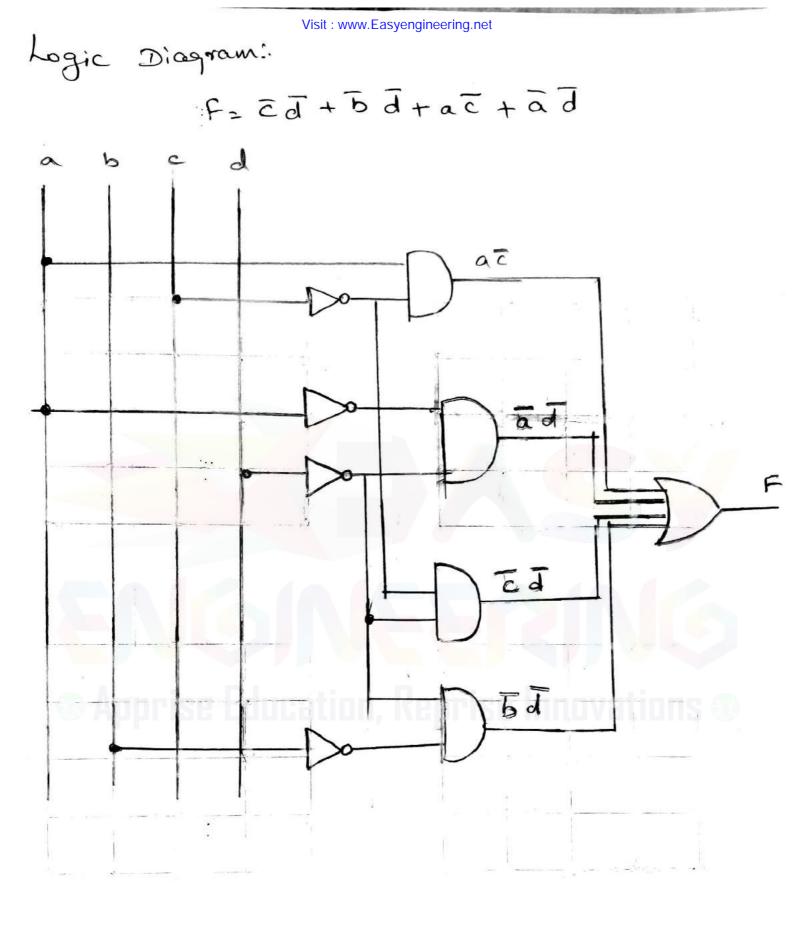

Simplify the Boolean Function Using k-map and implement using only NAND gates F(A, B, C, D) = Sm(0, 8, 11, 12, 15) + Ed (1, 2, 4, 7, 10, 14) Make the essential and non-essential Prime implicants. (8) [N/D'15]

|   | A  | B  |   | C   | _   | Э | Y | - |   |   |

|---|----|----|---|-----|-----|---|---|---|---|---|

|   | 0  | 0  |   | 0   | 0 0 |   | 1 |   |   |   |

|   | 0  | 0  |   | 0   |     | 1 | × |   |   |   |

|   | 0  | 0  |   | I   |     | 0 | × |   |   |   |

|   | 0  | 0  |   | 1   |     | Ţ | 0 |   |   |   |

|   | 0  | L. |   | 0   |     | 0 |   | 0 | x |   |

|   | 0  | l  |   | + + |     | 0 |   | 1 | 0 | 1 |

|   | o  | l  |   | 1   |     | 0 | 0 |   |   |   |

| Ī | ю  | l  |   | ł   | 1   | j | × | 1 |   |   |

|   | Ĩ, | σ  |   | o   |     | 0 | 1 |   |   |   |

|   | I  | 0  | Ţ | σ   |     | 1 | 0 |   |   |   |

|   | 1  | 0  |   | 1   |     | υ | × | Ĭ |   |   |

|   | /  | O  |   | I   |     | ŀ | 1 |   |   |   |

|   | 1  | 1  |   | 0   |     | 0 | 1 |   |   |   |

| 1 | 1  | 1  |   | Ø   |     | 1 | 0 |   |   |   |

|   | )  | (  |   | /   |     | 0 | x |   |   |   |

|   | 1  | J  |   | 1   |     | J | 1 |   |   |   |

Essential Prine Implicants:

AC, AD

Non-evential Brine Implicants

Q &

# ENGNEERNG

Visit : wSvannedoby GamScanner

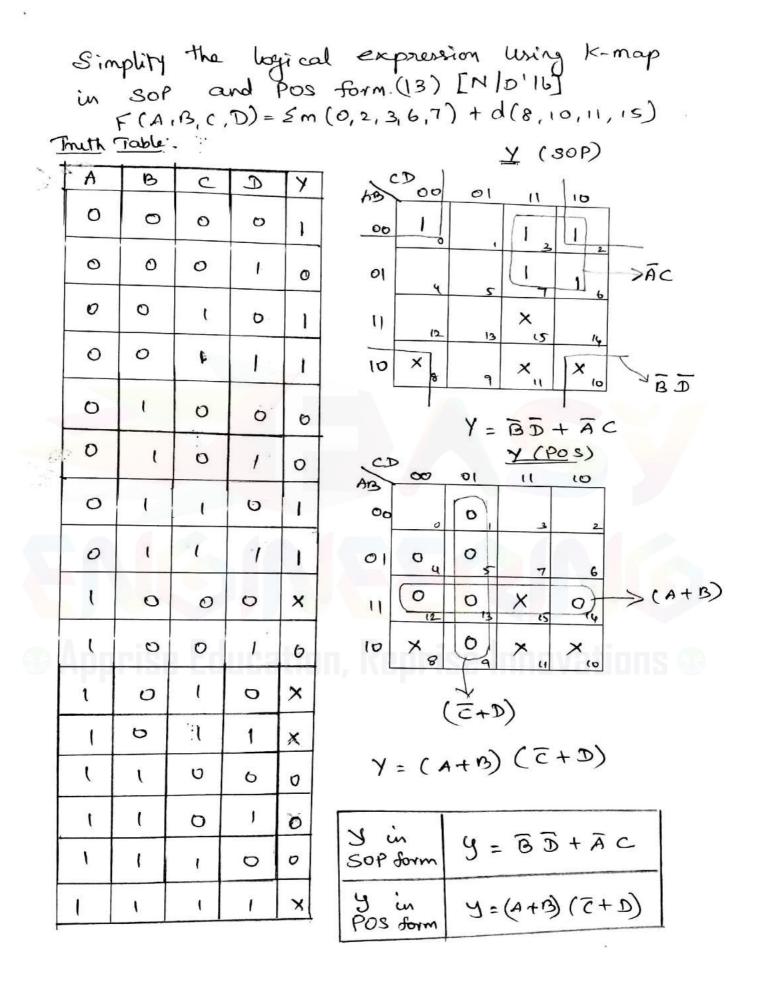

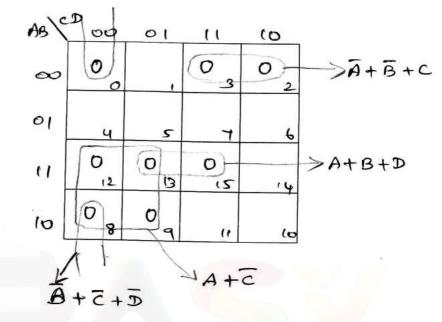

Reduce the following function using

$$k - nop$$

$F(A, B, C, D) = \Pi M(0, 2, 3, 8, 9, 12, 13, 15)$

(8)  $[A/M'15]$

|   | ^ |   | ß  | >   | (   | 2 | D   |   | Y   |  |   |

|---|---|---|----|-----|-----|---|-----|---|-----|--|---|

|   | ť |   | U  |     | c   | ) | 0   |   | D   |  |   |

|   | 0 |   | 0  |     | Ø   |   | 1   |   | È   |  |   |

|   | U |   | 0  |     | ::! |   | 0   |   | 0   |  |   |

|   | 0 |   | 0  |     | 1   |   | ,   |   | Ó   |  |   |

|   | 0 |   | -1 |     | 0   |   | 0   |   | 0   |  | Ł |

|   | D |   | 1  |     | 0   |   | - 1 |   | 1   |  |   |

|   | D |   | 1  |     | 1   |   | 1   |   | 0   |  | 1 |

|   | Ø |   | 1  | *** | 1   |   | 1   |   | ,   |  |   |

|   | 1 | ( | 3  |     | 0   |   | 0   |   | D   |  |   |

|   | Ť | C | )  | 15  | 0   |   | 1   |   | 0   |  |   |

|   | 1 | c | 2  |     | 1   |   | 0   |   | ŀ   |  |   |

|   | 1 | C | ,  | 1   |     | 1 |     | , |     |  |   |

|   | 1 | 1 |    |     | 0   |   | Ø   |   | 0   |  |   |

|   | , | / |    |     | 0   |   | 1   |   | D   |  |   |

|   |   | 1 |    | 1   |     | - | σ   |   | , [ |  |   |

| / |   | 1 |    | 1   |     |   | 1   |   | D   |  |   |

$F = (\overline{A} + \overline{B} + c) (A + \overline{c}),$   $(\overline{B} + \overline{c} + \overline{D}) (A + B + \overline{P})$

Reprise

Visit : wScangedgby=@amScanner

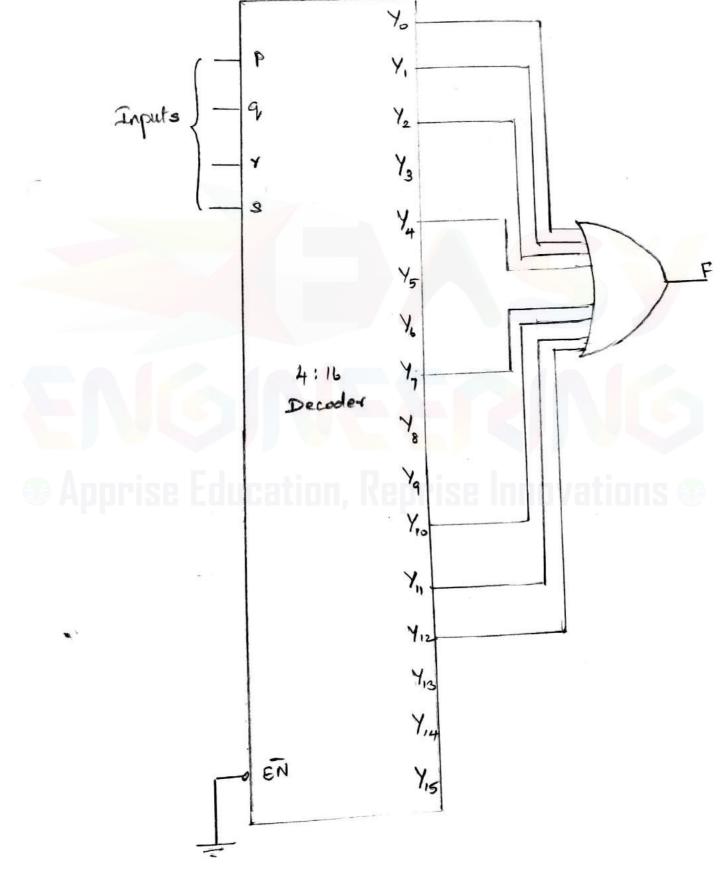

· Implement the quantion :  $F(P, q, r, s) = \Xi(0, 1, 2, 4, 7, 10, 11, 12)$  Using decoder. (8) [N] D'14]

Visit : wScannedoby GamScanner

Minimize the function  $F(a,b,c,d) = \Xi(0,4,6,8,9,10,12)$ with  $d = \Xi(2,13)$ . Simplement the quantion using only NOR gates (8) [N/D'14]

Visit : wScannedgby GamScanner

### Visit : www.Easyengineering.net EE6301 – DIGITAL LOGIC CIRCUITS UNIT - III SYNCHRONOUS SEQUENTIAL CIRCUITS Part - A

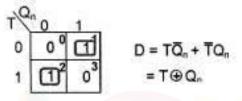

- 1. Convert T flip into D Flip flop [A/M-2015]

- 1. Truth Table for T Flip Flop

| Input | Outputs |                  |  |

|-------|---------|------------------|--|

| Т     | Qn      | Q <sub>n+1</sub> |  |

| 0     | 0       | 0                |  |

| 0     | 1       | 1                |  |

| 1     | 0       | 1                |  |

| 1     | 1       | 0                |  |

3. Conversion Table

| Т | Q, | Q <sub>n+1</sub> | D |

|---|----|------------------|---|

| 0 | 0  | 0                | 0 |

| 0 | 1  | 1                | 1 |

| 1 | 0  | 1                | 1 |

| 1 | 1  | 0                | 0 |

2. Excitation Table for D Flip Flop

| Out | tputs | Input<br>D |  |

|-----|-------|------------|--|

| Q.  | Q1    |            |  |

| 0   | 0     | 0          |  |

| 0   | 1     | 1          |  |

| 1   | 0     | 0          |  |

| 1   | 1     | 1          |  |

K-map Simplification

- State the rules for state assignment [A/M-2015]

- States which have the same next state, for a given input, should be given adjacent assignments

- States which are the next states of the same state should be given adjacent assignments .

- To simplify the output function, states which have the same output for a given input should be . given adjacent assignments.

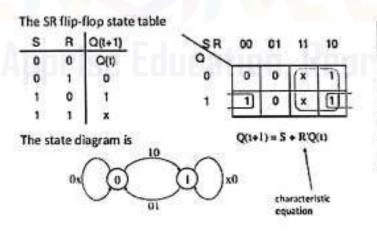

- Draw the truth table and state diagram of SR flip-flop [N/D-2015]

| S | R | Q              | State     |

|---|---|----------------|-----------|

| 0 | 0 | Previous State | No change |

| 0 | 1 | 0              | Reset     |

| 1 | 0 | 1              | Set       |

| 1 | 1 | ?              | Forbidden |

Draw the state diagram of JK flip flop. [N/D-16]

5. What is edge triggered flip flops? [N/D-2015]

An edge-triggered flip-flop changes states either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock pulse on the control input.

| Inp | Inputs |   | puts |          |

|-----|--------|---|------|----------|

| D   | C      | Q | Q'   | Comments |

| 0   | î      | 0 | 1    | RESET    |

| 1   | 1      | 1 | 0    | SET      |

If there is a HIGH on the D input when a clock pulse is applied, the flip-flop SETs and stores a 1. If there is a LOW on the D input when a clock pulse is applied, the flip-flop RESETs and stores a 0.

State any two differences between Moore and Mealy state machines.[M/J-2016] [N/D-16]

|     | Mealy                                                               | Moore                                                                                                                                                                            |

|-----|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (1) | O/Ps depend on the present<br>state and present I/Ps                | O/Ps depend only on the<br>present state                                                                                                                                         |

| (2) | The O/P changes asyn<br>-chronously with the<br>enabling clock edge | Since the O/Ps change<br>when the state changes,<br>and the state change is<br>synchronous with the<br>enabling clock edge, O/Ps<br>change synchronously<br>with this clock edge |

| (3) | A counter is not a Mealy<br>machine                                 | A counter is a Moore<br>machine (o/ps = state bits)                                                                                                                              |

7. Give the Characteristic equation and characteristic table of SR flip-flop.[M/J-2016]

| Characteristic table of | SR flip-flop: |

|-------------------------|---------------|

|-------------------------|---------------|

| S | R | Qn | Qn+1 | State     |  |

|---|---|----|------|-----------|--|

| 0 | 0 | 0  | 0    | No Change |  |

| 0 | 0 | 1  | 1    | No Change |  |

| 0 | 1 | 0  | 0    | Reset     |  |

| 0 | 1 | 1  | 0    | Reset     |  |

| 1 | 0 | 0  | 1    | Set       |  |

| 1 | 0 | 1  | 1    | Joer      |  |

| 1 | 1 | 0  | X    | Invalid   |  |

| 1 | 1 | 1  | X    | Invalio   |  |

Characteristic equation of SR flip-flop

$$Q_{n+1} = S + R'Q_n$$

#### UNIT - III Part - B

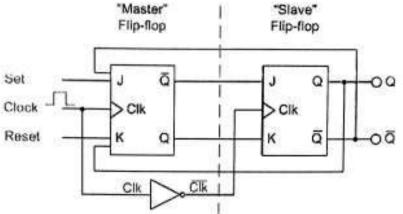

- 1. Explain the operation of a master slave JK flip flop (8) [A/M-2015], [M/J-2016]

- Master-slave flip flop is designed using two separate flip flops.

- Out of these, one acts as the master and the other as a slave. The figure of a master-slave J-K flip flop is shown below.

- Both the J-K flip flops are connected in a series connection.

- The output of the master J-K flip flop is fed to the input of the slave J-K flip flop.

- The output of the slave J-K flip flop is given as a feedback to the input of the master J-K flip flop.

- The clock pulse [Clk] is given to the master J-K flip flop and it is sent through a NOT Gate and thus inverted before passing it to the slave J-K flip flop.

#### Operation

- When Clk=1, the master J-K flip flop gets disabled. The Clk input of the master input will be the opposite of the slave input. So the master flip flop output will be recognized by the slave flip flop only when the Clk value becomes 0.

- When the clock pulse males a transition from 1 to 0, the locked outputs of the master flip flop are fed through to the inputs of the slave flip-flop making this flip flop edge or pulse-triggered.

- Thus, the circuit accepts the value in the input when the clock is HIGH, and passes the data to the output on the falling-edge of the clock signal.

- This makes the Master-Slave J-K flip flop a Synchronous device as it only passes data with the timing of the clock signal.

Visit : www.Easyengineering.net

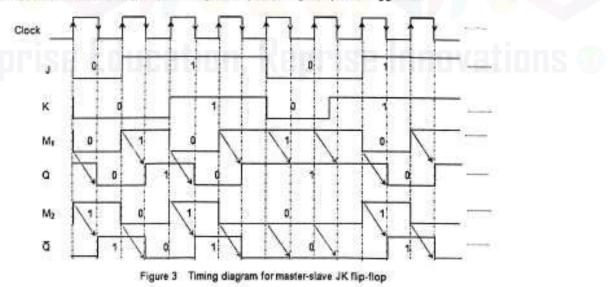

- Design a 3-bit bidirectional shift register. (8) [A/M-2015]

- The above diagram shows 3-bit Bi-directional Shift register, this type of register allows shifting of data either to the left side or to the right side.

- It is implemented by using logic gate circuitry that enables the transfer of data from one stage to the next stage to left or to the right, depending on the level of a control line.

- The RIGHT/LEFT-----RIGHT/LEFT\_ is the control input signal which allows data shifting either towards right or towards left. A high on this line enables the shifting of data towards right and a low enables it towards left.

- When RIGHT/LEFT-----RIGHT/LEFT\_ signal is high, out of the pair of each 2 AND gates the first AND gate from each of the pair is enabled.

- The state of the Q output of each Flip Flop is passed through the input of the following flip flop. When the clock pulse arrives, the data are shifted one place to the right.

- When RIGHT/LEFT-----RIGHT/LEFT\_ signal is low, out of the pair of each 2 AND gates the second AND gate from each of the pair is enabled.

- The state of the Q output of each Flip Flop is passed through the input of the preceding flip flop. When the clock pulse arrives, the data are shifted one place to the left.

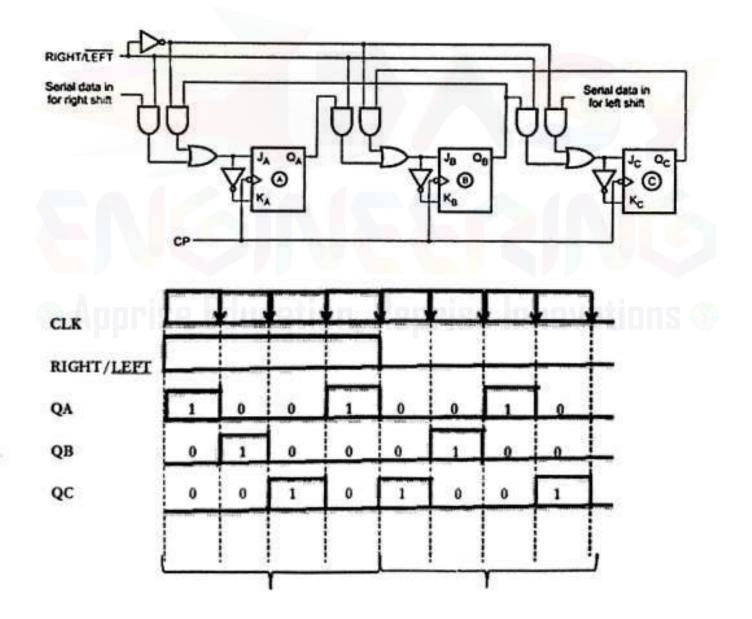

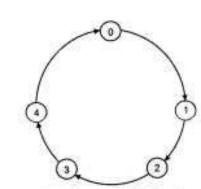

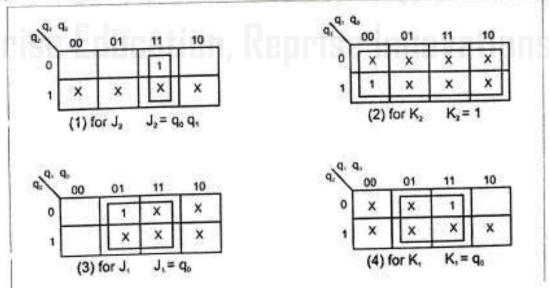

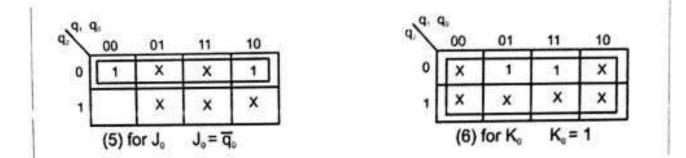

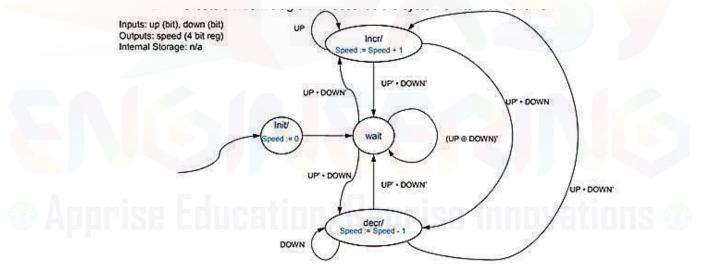

3. Design a MOD-5 synchronous counter using JK flip-flops (8) [A/M-2015]

State Diagram of Mod - 5 Counter

State Table:

State Diagram:

|    | Excitation Inputs |                |    | NS             |            |                | PS |                |                |    |                |

|----|-------------------|----------------|----|----------------|------------|----------------|----|----------------|----------------|----|----------------|

| Ko | Jo                | K <sub>1</sub> | J1 | K <sub>2</sub> | $J_2$      | Q <sub>0</sub> | Q1 | Q <sub>2</sub> | q <sub>0</sub> | q1 | q <sub>2</sub> |

| X  | 1                 | X              | 0  | X              | 0          | 1              | 0  | 0              | 0              | 0  | 0              |

| 1  | X                 | X              | 1  | X              | 0          | 0              | 1  | 0              | 1              | 0  | 0              |

| X  | 1                 | 0              | X  | X              | 0          | 1              | 1  | 0              | 0              | 1  | 0              |

| 1  | x                 | 1              | X  | X              | 1          | 0              | 0  | 1              | 1              | 1  | 0              |

| x  | 0                 | x              | 0  | 1              | x          | 0              | 0  | 0              | Ó              | 0  | 1              |

|    |                   |                |    |                | (manufact) |                |    | 1000           |                |    | 2              |

| X  | X                 | X              | X  | X              | X          | X              | X  | X              | 1              | 0  | 1              |

| X  | X                 | X              | X  | X              | X          | X              | X  | X              | 0              | 1  | 1              |

| X  | х                 | X              | X  | X              | X          | X              | X  | X              | 1              | 1  | 4              |

K-map simplification

Visit : www.Easyengineering.net

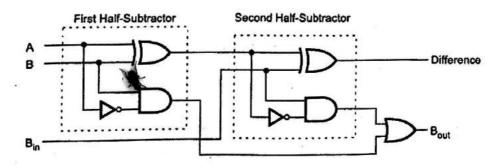

# Logic Diagram:

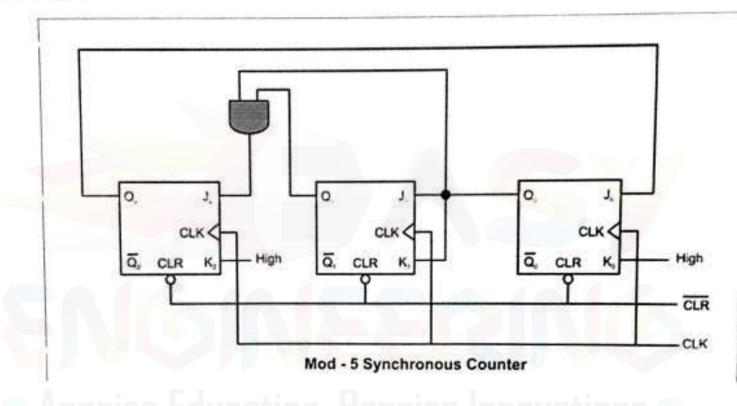

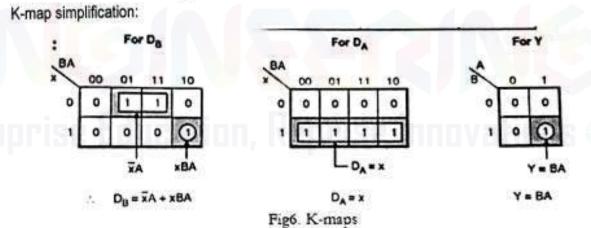

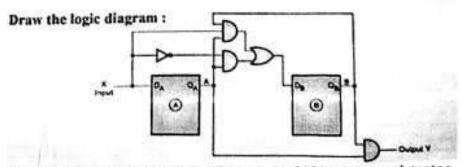

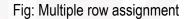

# 4. Design a sequence detector to detect the sequence 101 using JK flip flop (8) [A/M-2015]

State Diagram

Fig3. State diagram for 101 detector

State table

| Present state      | Next | state | Output |       |  |

|--------------------|------|-------|--------|-------|--|

| and the second day | x=0  | x=1   | x = 0  | x = 1 |  |

| a                  | a    | b     | 0      | 0     |  |

| b                  | c    | b     | 0      | 0     |  |

| c                  | a    | d     | 0      | 1     |  |

| d                  | c    | b     | 0      | 0     |  |

## Fig4. State table for above state diagram

Excitation table:

| laput<br>X | Pres | cut state | Next<br>B+1 | state<br>A+1 | F/F is<br>D | nputs<br>D <sub>A</sub> | Output |

|------------|------|-----------|-------------|--------------|-------------|-------------------------|--------|

| 0          | 0    | 0 (a)     | 0           | 0 (a)        | 0           | 0                       | 0      |

| 0          | 0    | 1 (b)     | 1           | 0 (c)        | 1           | 0                       | 0      |

| 0          | 1    | 0 (c)     | 0           | 0 (a)        | 0           | 0                       | 0      |

| 0          | 1    | 1 (d)     | 1           | 0 (c)        | 1           | 0                       | 0      |

| 1          | 0    | 0 (a)     | 0           | 1 (b)        | 0           | 1                       | 0      |

| 1          | 0    | 1 (b)     | 0           | 1 (b)        | 0           | 1                       | 0      |

| 1          | 1    | 0 (c)     | 1           | 1 (d)        | 1           | 1                       | 0      |

| 1          | 1    | 1 (d)     | 0           | 1 (b)        | 0           | 1                       | 1      |

Fig5. Excitation table

Logic Diagram:

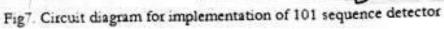

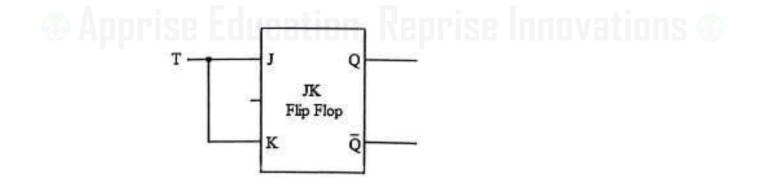

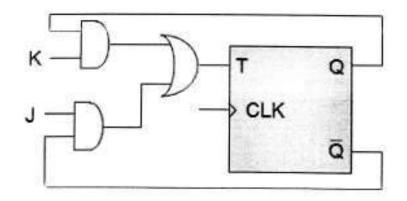

5. Realize T flip flop using JK flip flop. (4) [N/D - 2015] ,

State Table

| T | Qn | Qn+1 | J | ĸ |

|---|----|------|---|---|

| 0 | 0  | 0    | 0 | x |

| 0 | 1  | 1    | х | 0 |

| 1 | 0  | 1    | 1 | x |

| 1 | 1  | 0    | x | 1 |

K-map simplification

Logic Diagram

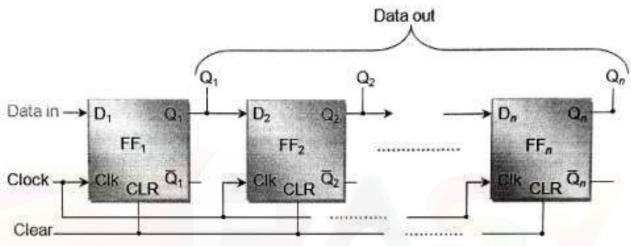

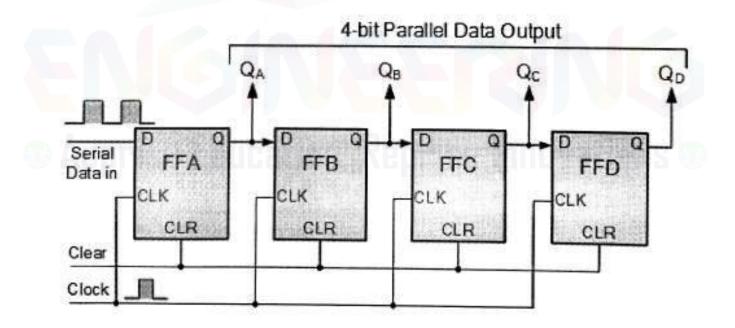

- 6. Write short notes on SIPO and draw the output waveform.(6) [N/D-16]

- In Serial In Parallel Out (SIPO) shift registers, the data is stored into the register serially while it is retrieved from it in parallel-fashion.

- Figure 1 shows an n-bit synchronous SIPO shift register sensitive to positive edge of the clock pulse.

- The data word which is to be stored (Data in) is fed serially at the input of the first flip-flop (D1 of FF1).

- It is also seen that the inputs of all other flip-flops (except the first flip-flop FF1) are driven by the outputs

of the preceding ones say for example, the input of FF2 is driven by the output of FF1.

- In this kind of <u>shift register</u>, the data stored within the register is obtained as a parallel-output data word (Data out) at the individual output pins of the flip-flops (Q<sub>1</sub> to Q<sub>n</sub>).

Figure 1 n-bit Serial-In Parallel-Out Right-Shift Shift Register

- In general, the register contents are cleared by applying high on the clear pins of all the flip-flops at the initial stage. After this, the first bit, B<sub>1</sub> of the input data word is fed at the D<sub>1</sub> pin of FF<sub>1</sub>.

- This bit (B<sub>1</sub>) will enter into FF<sub>1</sub>, get stored and thereby appears at its output Q<sub>1</sub> on the appearance of first leading edge of the clock. Further at the second clock tick, the bit B<sub>1</sub>right-shifts and gets stored into FF<sub>2</sub> while appearing at its output pin Q<sub>2</sub> while a new bit, B<sub>2</sub>enters into FF<sub>1</sub>.

- Similarly at each clock tick the data within the register moves towards right by a single bit while a new bit

of the input word enters into the register. Meanwhile one can extract the bits stored within the register in

parallel-fashion at the individual flip-flop outputs.

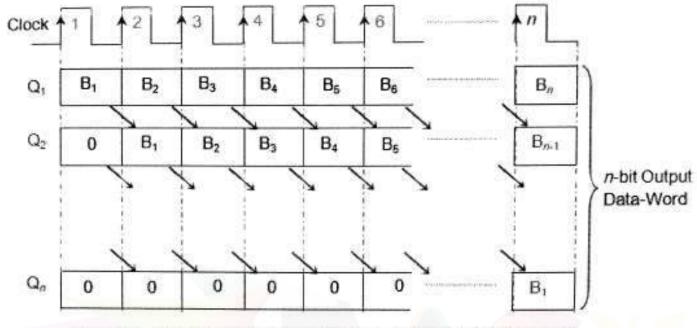

- Analyzing on the same grounds, one can note that the n-bit input data word is obtained as an n-bit output data word from the shift register at the rising edge of the n<sup>th</sup> clock pulse. This working of the shift-register an be summarized as in Table I and the corresponding wave forms are given by Figure 2.

| Clock Cycle | Data in | Q1               | Q2     |    |        | Q   |

|-------------|---------|------------------|--------|----|--------|-----|

| 1           | B1      | + B1             | 0,     |    | (22.4) | 0   |

| 2           | B2-     | · B2 、           | * B1   | 1. | 3442   | 140 |

| 3           | B3-     | · B3 .           | * B2   | 1. |        | 20  |

| 4           | B4-     | + B4             | * B3.  | La | 1015   | 20  |

| 5           | B5      | + Bs             | B4 .   | 12 | 22.5   | 20  |

| 6           | Be      | * B8             | N 85   |    |        | 20  |

|             |         |                  | × .    | ×  |        | У.  |

| 5.          |         | - 23             | 1      |    | 2442   | 1.1 |

|             | 1.00    |                  | 3 8:24 |    |        |     |

| n           | B       | → B <sub>n</sub> | *B_n-1 | 12 |        | ×B1 |

Table I Data Movement in Right-Shift SIPO Shift Register

Output of SIPO (right-shift) Shift Register

# Output Waveform

Logic Diagram

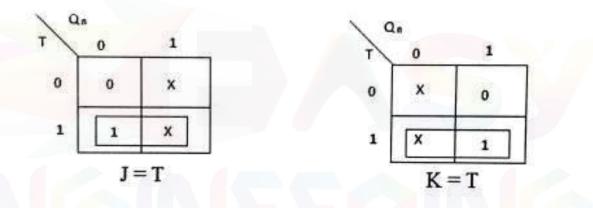

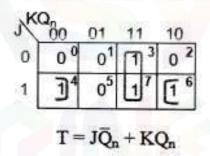

- 7. Explain the realization of JK flip flop from T flip flop. (7) [N/D-16]

- 1. Truth Table for JK Flip Flop

| Inp | uts | Out            | tputs |

|-----|-----|----------------|-------|

| J   | ĸ   | Q <sub>n</sub> | Qatt  |

| 0   | 0   | 0              | 0     |

| 0   | 0   | 1              | 1     |

| 0   | 1   | 0              | 0     |

| 0   | 1   | 1              | 0     |

| 1   | 0   | 0              | 1     |

| 1   | 0   | 1              | 1     |

| 1   | 1   | 0              | 1     |

| 1   | 1   | 1              | 0     |

3. Conversion Table

| J    | к | <b>Q</b> <sub>n</sub><br>0 | Qn+1 | Т |

|------|---|----------------------------|------|---|

| 0    | 0 | 0                          | 0    | Ũ |

| 0    | 0 | 1                          | 1    | 0 |

| 0000 | 1 | 0                          | 0    | 0 |

| 0    | 1 | 1                          | 0    | 1 |

| 1    | 0 | 0                          | 1    | 1 |

| 1    | 0 | 1                          | 1    | 0 |

| 1    | 1 | 0                          | 1    | 1 |

| 1    | 1 | 1                          | 0    | 1 |

2. Excitation Table for T Flip Flop

| Ou | tputs            | Input |

|----|------------------|-------|

| Qn | Q <sub>n+1</sub> | Т     |

| 0  | 0                | 0     |

| 0  | 1                | 1     |

| 1  | 0                | 1     |

| 1  | 1                | 0     |

4. K-map Simplification

👁 Apprise Education, Keprise Innovations 👁

# 5. Circuit Design

#### EE8351 – DIGITAL LOGIC CIRCUITS UNIT – IV ASYNCHRONOUS SEQUENTIAL CIRCUITSAND PROGRAMMABLE LOGIC DEVICES PART – A

- What is deadlock condition? [N/D'14] A condition resulting when one task is waiting to access a resource that another is holding, and vice versa.

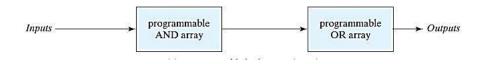

- 2. Draw the block diagram of PLA. [N/D'14]

State the difference between static – 0 and static – 1 hazard.[A/M'15] Static-1 Hazard: the output is currently 1 and after the inputs change, the output momentarily changes

to 0 before settling on 1

Static-0 Hazard: the output is currently 0 and after the inputs change, the output momentarily changes to 1 before settling on 0

4. What is a PROM? [A/M'15] , [N/D'15]

PROM- Programmable Read Only Memory is a device that contains Fixed AND and Programmable

OR functions. IT contains fuses inact giving all 1's in the stored bits and blown fuses by applying high voltage defining 0 states.

5. Compare pulsed mode and fundamental mode asynchronous circuit.[N/D'15]

| S.No. | Pulsed mode asynchronous circuit                                        | Fundamental mode asynchronous circuit    |

|-------|-------------------------------------------------------------------------|------------------------------------------|

| 1.    | Inputs are levels.                                                      | Inputs are pulses.                       |

| 2.    | Memory elements are either clocked flip – flops or time delay elements. | Memory elements are clocked flip – flops |

| 3.    | More difficult to dsign.                                                | Easy to design.                          |

- 6. What are the two types of asynchronous sequential circuits? [M/J'16] The two types of asynchronous sequential circuits are:

- a) Fundamental mode circuits

- b) Pulse mode circuits

7. State the difference between PROM, PLA and PAL. [M/J'16], [A/M'17]

| Types of PLD s | AND array    | OR array     |

|----------------|--------------|--------------|

| PROM           | Fixed        | Programmable |

| PLA            | Programmable | Programmable |

| PAL            | Programmable | Fixed        |

- 8. What is static hazard and dynamic hazard?[N/D'16]

- Static Hazard Output value the same after input change

Dynamic Hazard – Output value different after input change

- 9. Define races in asynchronous sequential circuits.[N/D'16] When 2 or more binary state variables change their value in response to a change in an input variable, race condition occurs in an asynchronous sequential circuit. In case of unequal delays, a race condition may cause the state variables to change in an unpredictable manner.

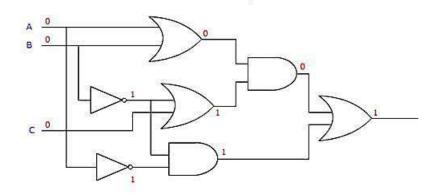

- 10. What is a flow table? Give example. [A/M'17]

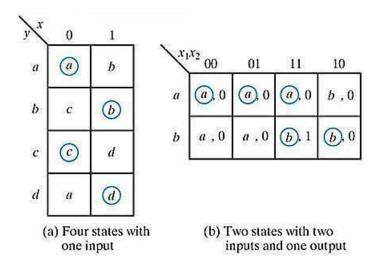

A state transition table with its internal state being symbolised with letters. Examples:

#### PART – B

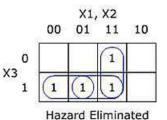

1. Explain the various types of hazards in sequential circuit design and the methods to eliminate them. Give suitable examples. (16) [N/D'14]

Hazards in any system are obviously an un-desirable effect caused by either a deficiency in the system or external. Influences. In digital logic hazards are usually referred to in one of three ways:

- a) Static Hazards

- b) Dynamic Hazards

- c) Function Hazards

These logic hazards are all subsets of the same problem: - When changes in the input variables do not change the output due to some form of delay caused by logic elements (NOT, AND, OR gates etc), this results in the logic not performing its function properly.

This is however a temporary problem, and the logic will finally come to the desired function. Despite the logic arriving at the correct output, it is imeritive that hazards be eliminated as they can have an effect on other systems. Imagine hazards like this in a piece of hospital equipment.

### Static Hazards

Definition:- "When one input variable changes, the output changes momentarily when it shouldn't" This particular type of hazard is usually due to a NOT gate within the logic. We can see the effects of the delay in the circuit from the following flash animation.

The hazard can be dealt with in two ways:

- 1. Insert another (additional) delay to the circuit. This then eliminates the static hazard.

- 2. Eliminate the hazard by inserting more logic to counteract the effects (Note this makes assumptions that the logic will fail)

- The first case is the most used of the two options. This is because it does not make assumptions about the logic, instead the method adds redundancy to overcome the hazard.

- To solve the hazard we shall use our previous example and apply a theory that 'Huffman' discovered.

- The insertion of a redundant loop can eliminate a static hazard.

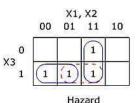

In the next example, it will also be evident that there will not be a situation where a static '0' occurs. A static '0' hazard is one which briefly goes to '1' when it should remain at '0'. A static '1' hazard is the reverse of this situation, i.e. the output should remain at '1' yet under some condition it briefly changes state to '0' (something we shall see in the following example)..

#### Example of Static Hazards

The Static '1' Hazard.

Let us consider an imperfect circuit that suffers from a delay in the physical logic elements i.e. AND gates etc.

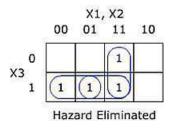

The simple circuit performs the function:

## f = X1.X2 + X1'.X3

and the logic diagram can be shown as follows:

At the starting diagram, it is clear that if no delays were to occur, then the circuit would function normally. However since this is not a perfect circuit, and an error occurs when the input changes from 111 to 011. i.e. When X1 changes state.

This Karnaugh Map shows the circuit. The two gates are shown by solid rings, and the hazard can be seen under the dashed ring. The theory proved by Huffman tells us that by adding a redundant loop 'X2X3' this will elimate the hazard. So the resulting logic is of the form shown in the next figure.

So our original function is now: f =X1.X2 + X1'.X3 + X2.X3

It is observed that even with imperfect logic elements, this example will not show signs of hazards when X1 changes state. This theory can be applied to any logic system.

#### **Dynamic Hazards**

- Definition:- "A dynamic hazard is the possibility of an output changing more than once as a result of a single input change"

- Dynamic hazards often occur in larger logic circuits where there are different routes to the output (from the input). If each route has a different delay, then it quickly becomes clear that there is the potential for changing output values that differ from the required / expected output.

e.g. A logic circuit is meant to change output state from '1' to '0', but instead changes from '1' to '0' then '1' and finally rests at the correct value '0'. This is a dynamic hazard.

- Dynamic hazards take a more complex method to resolve. The below example shows how a dynamic hazard can occur but now how to solve it.

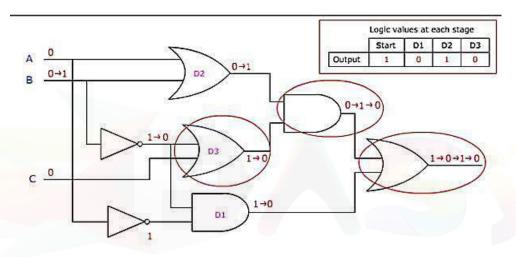

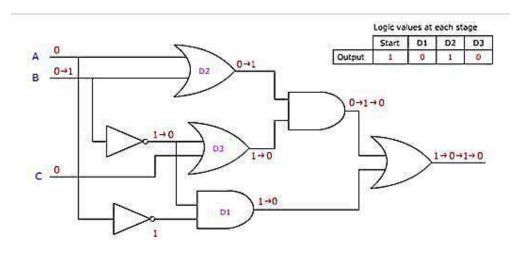

Let us take the circuit above, and see the proper logic output with the logic values above

Let artificial delays be introduced in some of the elements. Marked D1, D2 and D3.

• Consider D1 < D2 < D3.

i.e. The delay in D1 is less than the delay in D2, and the delay in D3 is greater than the delay in D2.

- Say that input B changes from 0 to 1. Working with one delay at a time the output can be determined.

- There could be a different output value for every different delay.

- The NOT gate shown changes from 1 to 0. Remembering that D1 is the shortest of the three delays, the AND gate shown will also change from 1 to 0.

- Because the other delays (D2, D3) are longer than D1, and because the other gates have no delay (or neglible delay), our output changes from 1 to 0. (The first effect of the hazard).

- The next delay to occur is D2. So the OR gate shown implements the change (0 OR 1 = 1). Now the AND gate has only seen the change in one of its inputs due to the delay D3 being longer than the other delays. So momentarily, both inputs are logic 1 which means the AND gates output goes to logic 1 hence changing the output of the entire circuit (1 OR 0 = 1).

- The next delay to occur is D3. The OR gate reacts slower than D1 to the change in input, but now the OR gate implements the change (0 OR 0 = 0). There is a knock on effect to the AND gate (as 0 AND 1 = 0) and then again to the output of the entire circuit. The output rests at 0.

- This is the final stage as there are no more delays in the circuit and therefore no more changes of state due to input B changing.

- D3(1 OR 0 = 1).

- The circuit finally rests at the correct logical value for an ideal circuit. However the output has changed values twice before coming to the correct result on the third change. If this was an ideal circuit then the output should have changed only once.

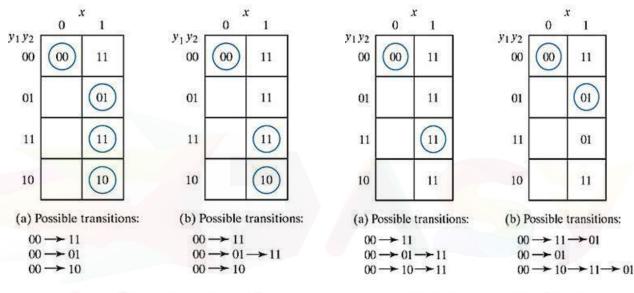

- 2. Describe with reasons the effect of races in asynchronous sequential circuit design. Explain its type with illustrations. Show the method of race free state assignments with examples. (16) [N/D'14]

- A race condition or race hazard is the behaviour of an electronic, software, or other system where the output is dependent on the sequence or timing of other uncontrollable events.

- A race condition may occur in a system of logic gates where inputs vary. If a given output depends on the state of the inputs it may only be defined for steady-state signals. As the inputs change state a small delay will occur before the output changes due to the physical nature of the electronic system. The output may, for a brief period, change to an unwanted state before settling back to the designed state. Certain systems can tolerate such glitches but if this output functions as a clock signal for further systems that contain memory, for example, the system can rapidly depart from its designed behaviour.

#### Types:

#### Critical and non-critical forms

- a) A *critical race condition* occurs when the order in which internal variables are changed determines the eventual state that the state machine will end up in.

- b) A *non-critical race condition* occurs when the order in which internal variables are changed does not determine the eventual state that the state machine will end up in.

- Static, dynamic, and essential forms

- a) A static race condition occurs when a signal and its complement are combined together.

- b) A dynamic race condition occurs when it results in multiple transitions when only one is intended. They are due to interaction between gates. It can be eliminated by using no more than two levels of gating.

- c) An essential race condition occurs when an input has two transitions in less than the total feedback propagation time. Sometimes they are cured using inductive delay line elements to effectively increase the time duration of an input signal.

Design techniques such as Karnaugh maps encourage designers to recognize and eliminate race conditions before they cause problems. Often logic redundancy can be added to eliminate some kinds of races.

#### **RACE -FREE STATE ASSIGNMENT**

- Once a reduced flow table has been derived for an asynchronous sequential circuit, the next step in the design is to assign binary variables to each stable state. This assignment results in the transformation of the flow table into its equivalent transition table.

- The primary objective in choosing a proper binary state assignment is the prevention of critical races. Critical races can be avoided by making a binary state assignment in such a way that only one variable changes at any given time when a state transition occurs in the flow table.

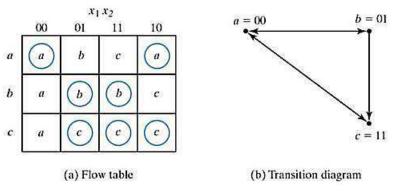

#### Three-Row Flow-Table Example

Fig: Three row flow table example

- To avoid critical races, we must find a binary state assignment such that only one binary variable changes during each state transition.

- An attempt to find such an assignment is shown in the transition diagram.

- State a is assigned binary 00, and state c is assigned binary 11.

- This assignment will ca use a critical race during the transition from a to c because there are two

changes in the binary state variables and the transition from a to c may occur directly or pass

through b.

- Note that the transition from c to a also ca uses a race condition, but it is noncritical because the transition does not pass through other states.

- A race-free assignment can be obtained if we add an extra row to the flow table. The use of a

fourth row does not increase the number of binary state variables, but it allows the formation of

cycles between two stable states.

- The transition table corresponding to the flow table with the indicated binary state assignment is shown in Fig. The two dashes in row d represent unspecified states that can be considered don'tcare conditions. However, care must be taken not to assign 10 to these squares, in order to avoid the possibility of an unwanted stable state being established in the fourth row.

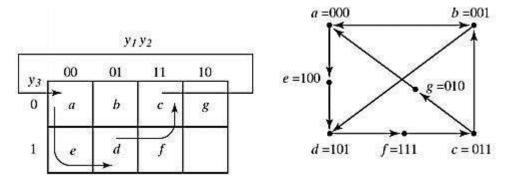

#### Four-Row Flow-Table Example

A flow table with four rows requires a minimum of two state variables. Although a race-free assignment is sometimes possible with only two binary state variables, in many cases the requirement of extra rows to avoid critical races will dictate the use of three binary state variables

Fig: Four-row flow-table example

- The following figure shows a state assignment map that is suitable for any four-row flow table. States a, b, c and d are the original states and e, f and g are extra states.

- The transition from a to d must be directed through the extra state e to produce a cycle so that only one binary variable changes at a time.

- Similarly, the transition from c to a is directed through g and the transition from d to c goes through f. By using the assignment given by the map, the four-row table can be expanded to a seven-row table that is free of critical races.

#### Fig: State assignment to modified flow table

Note that although the flow table has seven rows there are only four stable states. The uncircled states in the three extra rows are there merely to provide a race-free transition between the stable states.

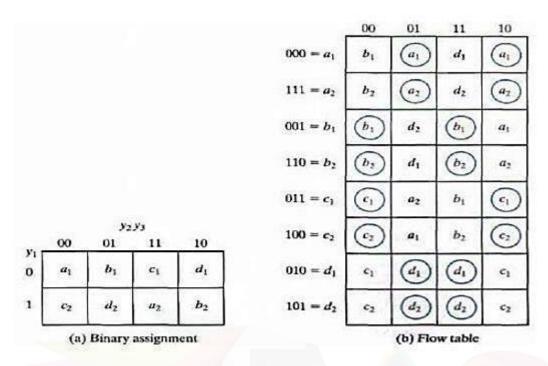

#### Multiple-Row Method

- The method for making race-free stale assignments by adding extra rows in the flow table is referred to as the shared-row method.

- A second method called the multiple-row method is not as efficient, but is easier to apply.

- In multiple- row assignment each state in the original row table is replaced by two or more combinations of state variables.

Fig: Multiple row assignment

- There are two binary state variables for each stable state, each variable being the logical complement of the other. For example, the original state a is replaced with two equivalent states a1 =000 and a2 = 111.

- The output values, not shown here must be the same in a1 and a2. Note that a1 is adjacent to b1, c2 and d1, and a2 is adjacent to c1, b2 and d2, and similarly each state is adjacent to three states with different letter designations.

- The expanded table is formed by replacing each row of the original table with two rows. In the multiple-row assignment, the change from one stable state 10 another will always cause a change of only one binary state variable.

- Each stable stale has two binary assignments with exactly the same output.

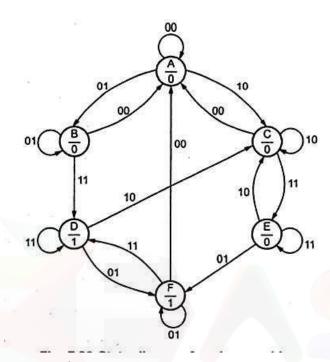

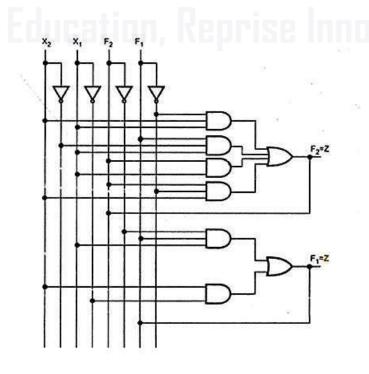

3. Design an asynchronous sequential circuit that has two inputs  $X_2$  and  $X_1$  and one output Z. When  $X_1 = 0$ , the output Z is 0. The first change in  $X_2$  that occurs while  $X_1$  is 1 will cause output Z to be 1. The output Z will remain 1 until  $X_1$  returns to 0.(16) [A/M'15]

State diagram

Primitive flow table constructed from state diagram

| Present<br>state | Next state .Output Z<br>for X <sub>2</sub> X <sub>1</sub> Inputs |                |             |     |  |  |

|------------------|------------------------------------------------------------------|----------------|-------------|-----|--|--|

| State            | 00                                                               | 01             | 11          | 10  |  |  |

| А                | A.0                                                              | в,-            |             | с   |  |  |

| в                | A                                                                | <b>B</b> .0    | D           |     |  |  |

| C                | Α,-                                                              |                | Е           | ©,0 |  |  |

| D                |                                                                  | F.,-           | <b>0</b> .1 | с,- |  |  |

| Ε                |                                                                  | F ,-           | (E).0       | с   |  |  |

| F                | Α                                                                | <b>(F)</b> , 1 | D           |     |  |  |

Flow table with state assignment

| Present state                 | Next state, Output Z<br>for X <sub>2</sub> X <sub>1</sub> Inputs |          |                |        |  |

|-------------------------------|------------------------------------------------------------------|----------|----------------|--------|--|

| F <sub>2</sub> F <sub>1</sub> | 00                                                               | 01       | 11             | 10     |  |

| s₀ <del>- •</del> 0 0         | S.0                                                              | (S.) . 0 | S <sub>2</sub> | S1     |  |

| S₁ <del>- +</del> 0 1         | S <sub>0</sub>                                                   | ,s,      | (S1).0         | (S) .0 |  |

| S₂ <del>→</del> 1 0           | s <sub>o</sub>                                                   | (S2. 1   | 52.1           | (s3)   |  |

| S <sub>3</sub> → 1 1          |                                                                  | \s2)     |                | (s,/   |  |

Flow table converted into a transition table

| Present state  |    | Next state, Output Z<br>for X <sub>2</sub> X <sub>1</sub> Inputs |      |      |      |  |

|----------------|----|------------------------------------------------------------------|------|------|------|--|

| F <sub>2</sub> | F1 | 00                                                               | 01   | 11   | 10   |  |

| 0              | 0  | 00,0                                                             | 00,0 | 10   | 01,- |  |

| 0              | 1  | 00,-                                                             | 11   | 01,0 | 01.0 |  |

| 1              | 0  | 00,-                                                             | 10.1 | 10.1 | 11   |  |

| 1              | 1  |                                                                  | 10   |      | 01,- |  |

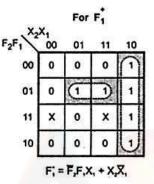

K-map simplification

For Z F2F 01 10 00 11 x x 0 0 00 x 01 x 0 0 11 X X 10 1 Z = F,

Logic diagram

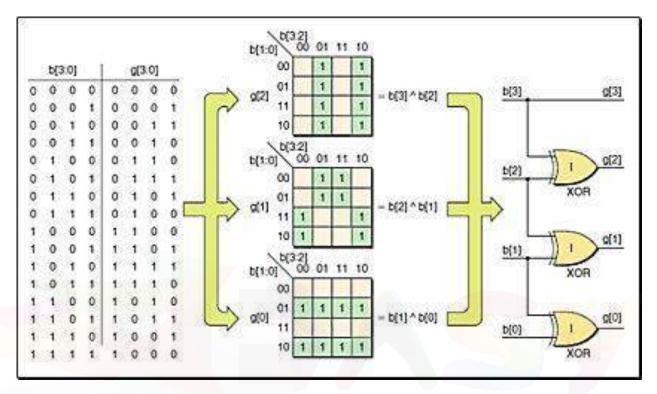

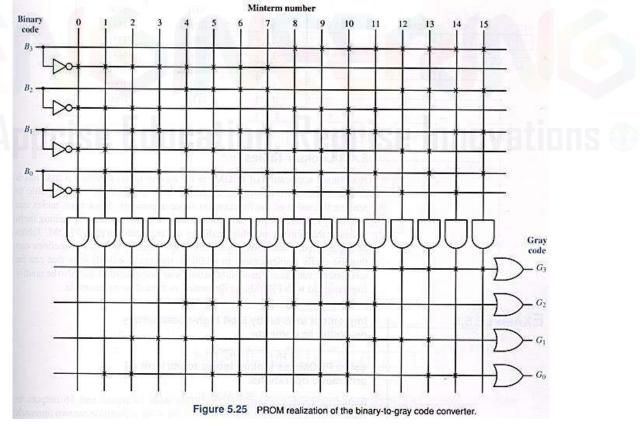

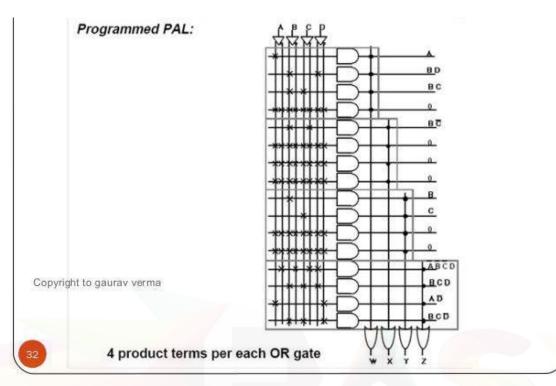

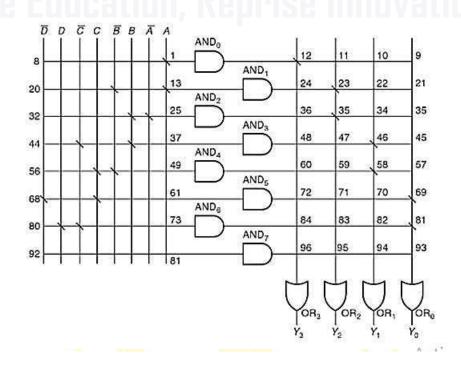

Show how to program the fusible links to get a 4 bit Gray code from the binary inputs using PLA and PAL and compare the design requirements with PROM. (16) [N/D'15] Gray code generator using PROM

PROM based binary to gray code converter

Binary to gray code converter Boolean expression are concluded as

$Y_3 = A$

$\begin{array}{l} Y_2 = A\overline{B} + \overline{A}B \\ Y_1 = B\overline{C} + \overline{B}C \\ Y_0 = C\overline{D} + \overline{C}D \\ \text{It is noted that } 4 \ge 7 \ge 4 \text{ PLA is needed to implement gray code converter and same for PAL also.} \\ \text{Total number of AND OR gates links are} \\ 96 - \text{PLA} \\ 56 - \text{PAL} \\ 64 - \text{PROM} \end{array}$

What are static – 0 and static – 1 hazard? Explain the removal of hazards using hazard covers in kmap. (8) [ M/J'16]

## **Static Hazards**

A static hazard occurs when a single input variable change should cause no change in the output of a combinational logic circuit, but a short glitch of the incorrect logic level occurs.

The problem occurs because real physical implementations of logic functions have finite propagation times which are variable, and if two inputs to a gate should theoretically change simultaneously, one will actually change before the other.

If more than one input variable changes "simultaneously" there is no way to guarantee that such glitches will not occur.

Types of Static Hazards

Static – 1 hazard :- A static 1 hazard may occur in a two level sum of products (SOP) implementation.

Static – 0 hazard :- A static 0 hazard may occur in a two level product of sums

(POS)implementation.

Example of Static Hazards

The Static '1' Hazard.

Let us consider an imperfect circuit that suffers from a delay in the physical logic elements i.e. AND gates etc.

The simple circuit performs the function:

f = X1.X2 + X1'.X3

and the logic diagram can be shown as follows:

At the starting diagram, it is clear that if no delays were to occur, then the circuit would function normally. However since this is not a perfect circuit, and an error occurs when the input changes from 111 to 011. i.e. When X1 changes state.

This Karnaugh Map shows the circuit. The two gates are shown by solid rings, and the hazard can be seen under the dashed ring. The theory proved by Huffman tells us that by adding a redundant loop 'X2X3' this will elimate the hazard. So the resulting logic is of the form shown in the next figure.

So our original function is now: f =X1.X2 + X1'.X3 + X2.X3

It is observed that even with imperfect logic elements, this example will not show signs of hazards when X1 changes state. This theory can be applied to any logic system.

- 6. Explain cycles and races in asynchronous sequential circuits. (8) [ M/J'16] Races in asynchronous sequential circuits

- Race condition: "two or more binary state variables will change value when one input variable changes "Cannot predict state sequence if unequal delay is encountered "

- Non-critical race: "The final stable state does not depend on the change order of state variables "Critical race:" The change order of state variables will result in different stable states.

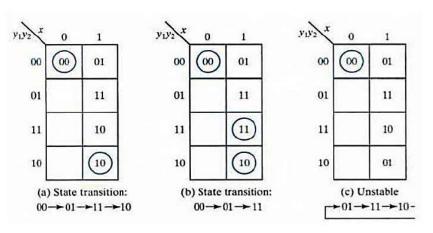

Fig. 9-7 Examples of Critical Races

Fig. 9-6 Examples of Noncritical Races

Cycles in asynchronous sequential circuits

- A cycle occurs when an asynchronous circuit makes a transition through a series of unstable states.

- When a state assignment is made so that it introduces cycles.

- Care must be taken so that each cycle terminates on a stable state.

- If a cycle does not contain a stable state, the circuit will go from one unstable state to another, until the inputs are changed.

Fig: Examples of cycles

## EE8351 – DIGITAL LOGIC CIRCUITS UNIT – V VHDL PART – A

- Write a VHDL code for 2 x 1 MUX. [N/D'14], [M/J'16], [A/M'17] library ieee; use ieee.std\_logic\_1164.all; entity mux2\_1 is port (a,b,sel:instd\_logic; c: out std\_logic); end mux2\_1; architecture muxarch of mux2\_1 is begin process (a,b,sel) begin if s='0' then c<=a;else s='1' then c<=b; end if; end process; end muxarch;

- State the advantage of package declaration over component declaration. [N/D'14]

Package declaration is used to declare components, types, constants, functions and so on.

Declared Packages will be shared by many design units.

Component declaration declares the name of the entity and interface of a component which is used

by the design unit. Declared Component will be used by the corresponding design unit.

- 3. What is a package in VHDL?[A/M'15] A VHDL package contains subprograms, constant definitions, and/or type definitions to be used throughout one or more design units. Each package comprises a "declaration section", in which the available (i.e. exportable) subprograms, constants, and types are declared, and a "package body", in which the subprogram implementations are defined, along with any internally-used constants and types.

- 4. Write the behavioural modelling code for a D flip flop.[A/M'15], [N/D'15], [N/D'16] Library ieee; use ieee.std\_logic\_1164.all; entity dff is port (D,clk,rst:instd\_logic; Q: out std\_logic); end dff; architecture behave of dff is begin process (rst,clk) Begin if rst='0' then Q<='0'; elseclock'event and clk='1' then Q<=D; end lf; end process; end behave;

- List out the operators present in VHDL.[N/D'15] Logical operators, Arithmetic operators, Relational operators and shift operators.

What is data flow modelling in VHDL? Give its basic mechanism.[M/J'16] A dataflow style architecture models the hardware in terms of the movement of data over

```

continuous time between combinational logic components such as adders, decoders and primitive logic gates.

```

```

Basic Mechanism:

entity entity_name is

port();

architecture dataflow of entity_name is

....

begin

...

end dataflow;

```

7. Write the VHDL code for a logic gate which gives high output only when both the inputs are high. [N/D'16]

```

entity andgate is

port(A:in std_logic;

B:in std_logic;

Y: in std_logic);

```

end andgate

Give the syntax for package declaration and package body in VHDL.[A/M'17] package package\_name is {package\_declarative\_item} end [package\_name];

package body package\_name is

{package\_declarative\_item}

end [package\_name];

9. What is the purpose of VHDL programming? Or what is the need for VHDL? [M/ J- 13] Very high speed integrated circuit hardware description language. It is a language for describing a hardware, which has to be readable for machines and humans at the same time & it structured and comprehensible code, so that the source code can serve as a kind of specification document. Thus it is used for studying digital logic circuits and testing its functions.

## PART – B

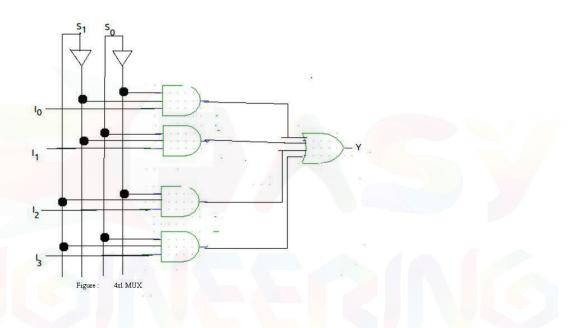

- 1. Write VHDL coding for 4 x 1 multiplexer. (7)[N/D'16]

- 4: 1 MUX

#### Truth Table:

| Input | S1 | SO | Ouptut |

|-------|----|----|--------|

| 10    | 0  | 0  | 10     |

| I1    | 0  | 1  | I1     |

| I2    | 1  | 0  | 12     |

| I3    | 1  | 1  | 13     |

## Logic Diagram:

```

Program:

```

end mux4x1 arch;

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity mux4x1 is

Port ( din : in STD_LOGIC_VECTOR (3 downto 0);

en : in STD LOGIC;

sel: in std logic vector(1 downto 0);

dout : out STD LOGIC);

end mux4x1;

architecture mux4x1 arch of mux4x1 is

signal iy:std logic;

-begin

with sel select

iy<=din(0) when "00",

din(1) when "01",

din(2) when "10",

din(3) when "11",

'0' when others;

dout<=iy when en='1' else '0';</pre>

```

- 2. Write the VHDL code to realise a full adder using (16)[A/M'15]

- 3. Write a VHDL program for full adder using structural modelling. (8) [N/D'15]

- 4. Explain in detail the concept of structural modelling in VHDL with an example of full adder. (13) [N/D'16]

- 5. Explain the concept of behavioural modelling and structural modelling in VHDL. Take the example of full adder design for both and write the coding.(8) [N/D'14]

Truth Table:

Logic Diagram

|   | А            | в                                                        | с                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Carry                                                                                     |                                                                                                          |      |          |    |                   |     |             |