# UNIT - 4

# ASYNCHRONOUS SEQUENTIAL CIRCUITS AND PROGRAMMABILITY LOGIC DEVICES

# 4.1 ASYNCHRONOUS SEQUENTIAL LOGIC CIRCUITS

In synchronous sequential circuits, the change of state occurs in response to the synchronized clock signal. But in asynchronous sequential circuits the change of state occurs when there is a change in input variable.

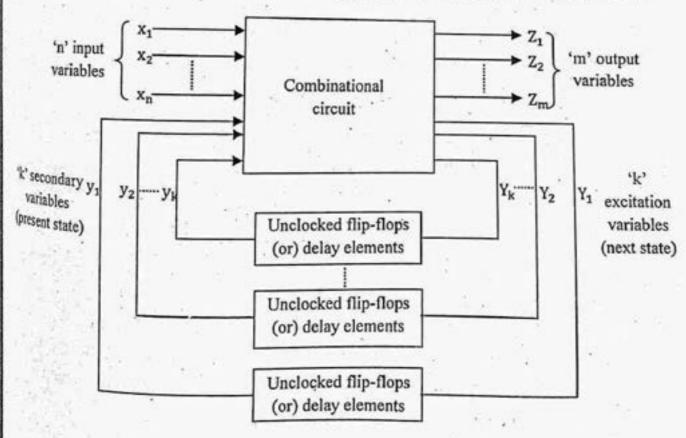

The memory elements of synchronous sequential circuits are clocked flipflops. The memory elements of asynchronous sequential circuits are either unclocked flip-flops or time delay elements. The asynchronous sequential circuit consists of a combinational circuit and delay elements connected to form feedback loops. There are 'n' input variables, 'm' output variables, 'k' present states and 'k' next states.

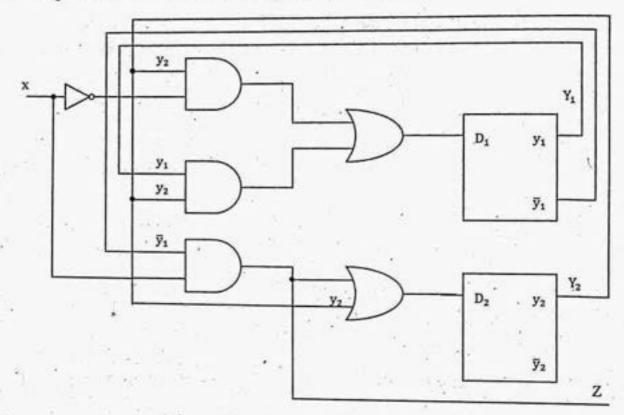

Figure 4.1 Asynchronous sequential circuit

The present states are called secondary variables. The next states are cal excitation variables. When an input variable 'x' changes, the secondary variable do not change instantaneously. It takes a certain amount of time because the sign has to propagate through the combinational circuit and delay elements. Hence time between two input changes is kept longer so that the circuit reaches a state.

After reaching a steady state condition both secondary variables (y) excitation variable (Y) are same. This is known to be a stable state. So asynchronous sequential circuits, because of unequal delays in the wires combinational circuits, it is impossible to have two or more input variable change exactly the same instant of time. Therefore simultaneous changes of two or m input variables are usually avoided. Only one input variable is allowed to change time.

Based on the input signals, the asynchronous sequential circuit is classified into,

- a. Fundamental mode sequential circuit.

- b. Pulse mode sequential circuit.

Assumptions that must be made for the fundamental mode circuit are,

- The input variable changes only when the circuit is stable.

- 2. Only one input variable can change at a given time.

- Inputs are levels and not pulses.

Assumptions that must be made for the pulse mode circuit are,

- The input variables are pulses instead of levels.

- 2. The width of the pulses is long enough for the circuit to respond to the input

- The pulse width must not be so long that it is still present after the new s is reached.

### 4.2 ANALYSIS OF ASYNCHRONOUS SEQUENTIAL LOGIC CIRCUITS.

### 4.2.1 Analysis of Fundamental mode sequential circuits

The behavior of an asynchronous sequential circuit can be found out from inputs, outputs and its states. The steps to analyze the asynchronous sequen circuit are,

step 1: Determine the next state equations and output equations. If there are any flipflops, use the respective characteristic equation to find the next state

Step 2: Plot the truth table.

The truth table should contain,

- Present state

- b. Input

- c. Next state

- d. Output

Step 3: From the truth table, plot the transition table.

Step 4: Assign states for the binary values and plot the state table.

Step 5: Plot the output map.

Step 6: Plot the state diagram.

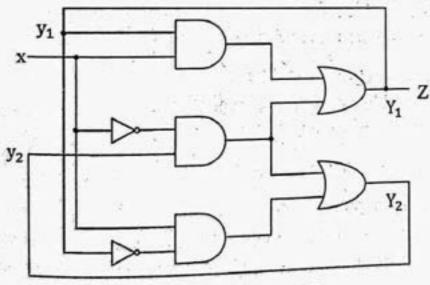

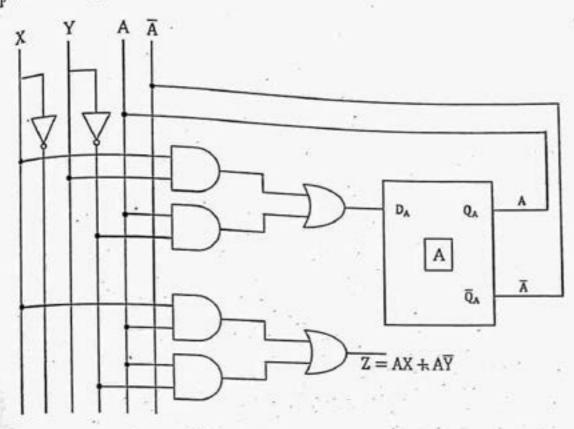

Consider the example shown in figure 4.2.

Figure 4.2

Step 1; Determine the next state equations and output equations.

Here the input is x, Present states are y<sub>1</sub> and y<sub>2</sub>, Next states are Y<sub>1</sub> and Y<sub>2</sub> and Output is Z

Next state equations:

$$Y_1 = y_1x + \overline{x}y_2$$

$$Y_2 = \overline{x}y_2 + x\overline{y}_1$$

$$Z = Y_1 \text{ or } Z = y_1x + \overline{x}y_2$$

Output equation:

Step 2: Plot the truth table.

The truth table should contain, Present states  $(y_1,y_2)$ , input (x), next states  $(Y_1,Y_2)$  and output (Z). Here the number of inputs is less than the number of present states. So write the input term first in the truth table which as shown in table 4.1.

First write the possible binary combination for present states and inputs. Then by substituting the value of x,  $y_2$  and  $y_1$  in the next state and output equations, find next states  $Y_2$ ,  $Y_1$  and output Z. For the given input, if the next state  $Y_2Y_1$  is same as that of  $y_2y_1$  then the state is said to be stable.

| Input Present |       | tstates          | Next states (  |                | es Output Sta |          |

|---------------|-------|------------------|----------------|----------------|---------------|----------|

| x             | У2    | , y <sub>1</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Z             |          |

| 0             | 0     | . 0              | 0              | 0              | 0             | Stable   |

| 0             | 0     | 1                | 0              | 0              | 0             | Unstable |

| 0 .           | 1     | 0                | 1              | 1              | 1             | Unstable |

| .0            | 1     | 1                | 1              | 1              | 1             | Stable   |

| 1             | . 0 . | 0                | 1              | 0              | . 0           | Unstable |

| 1             | 0     | 1                | 0              | 1.             | 1             | Stable   |

| 1.            | 1     | 0                | 1              | 0              | 0             | Stable   |

| 1             | 1     | 1                | 0              | 1              | 1             | Unstable |

Table 4.1 Truth table

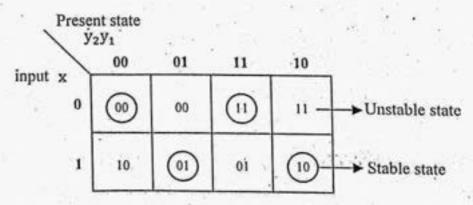

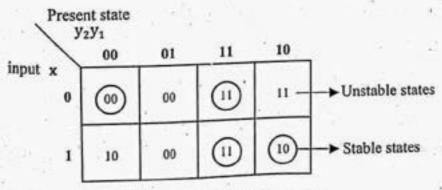

Step 3: Plot the transition table

Figure 4.3 Transition table

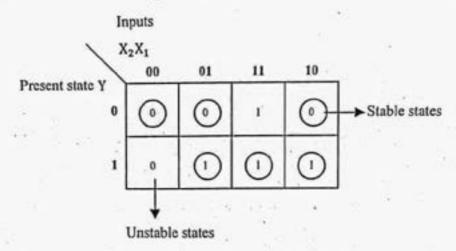

The rows of transition table represent input 'x' and columns of transition table represent present state  $y_2y_1$ . The number written in the table represents next state  $Y_2Y_1$ . The circle around  $Y_2Y_1$  indicate that the state is stable (present state and next state are same).

Step 4: Assign states for the binary values and plot the state table

Here present states and next states are 00, 01, 10 and 11. So assign a=00, b=01, c=10 and d=11. The state table can be drawn as shown in Figure 4.4.

|         |     | Present | state |   |

|---------|-----|---------|-------|---|

| input x | a   | b       | d     | c |

| 0       | (3) | a       | (d)   | d |

| 1       | С   | (P)     | ь     | 0 |

Figure 4.4 State table

Step 5: Plot the output map

| 1 | a . | b | d | c f |

|---|-----|---|---|-----|

| 0 | 0   |   | 1 | ÷   |

| 1 |     | 1 |   | 0   |

Figure 4.5 Output map

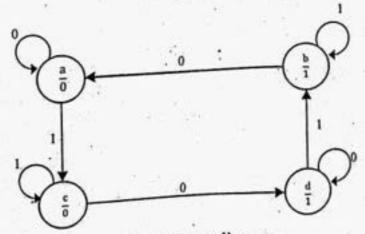

The output is mapped for all stable states which are indicated by circles as shown in figure 4.5. For unstable state, the output is mapped unspecified. By using the state table and output map, draw the next state transition for input x=0 and x=1 as shown in figure 4.6. Similarly mark the output Z from the output map for each stable state.

Figure 4.6 State diagram

### 4.2.2 Analysis of Pulse mode sequential circuits

Figure 4.7

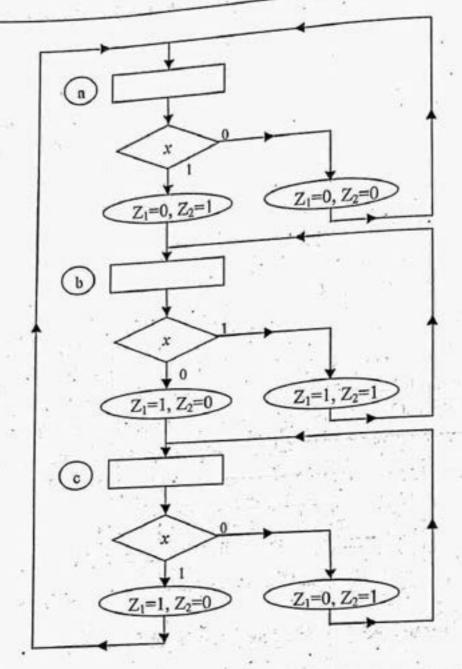

The analysis of pulse mode sequential circuit is same as that of fundamental mode sequential circuit. Consider the circuit shown in figure 4.7.

Step 1: Determine the next state equations and output equations.

Here the input is 'x', Present states are  $y_1$  and  $y_2$ , Next states are  $Y_1$  and  $Y_2$  and the Output is Z.

Next state equations:

$$Y_1 = D_1$$

(Characteristic equation of D flip-flop)

$Y_2 = D_2$

$D_1 = y_2 \overline{x} + y_1 y_2$  and  $D_2 = x \overline{y}_1 + y_2$

$Y_1 = y_2 \overline{x} + y_1 y_2$

$$Y_2 = x\overline{y}_1 + y_2$$

Output equation:

Here

Therefore,

$$Z = x\bar{y}_1$$

Step 2: Plot the truth table.

The truth table should contain, Present states  $(y_1, y_2)$ , input(x), Next states  $(Y_1, Y_2)$  and output (Z). Here the number of inputs is less than the number of present states. So write the input term first in the truth table as shown in table 4.2.

First write the possible binary combination for present state and inputs. Then by substituting the value of x,  $y_2$  and  $y_1$ , find the next states  $Y_2$ ,  $Y_1$  and output Z. For the given input, if the next state  $Y_2Y_1$  is same as that of present state  $y_2y_1$ , then the state is said to be stable.

| Input Preser |                | t states       | Next           | Next states Out |     | ·States  |

|--------------|----------------|----------------|----------------|-----------------|-----|----------|

| x            | y <sub>2</sub> | y <sub>1</sub> | Y <sub>2</sub> | Y <sub>1</sub>  | Z   | - 1      |

| 0            | .0             | 0              | 0              | 0               | 0 . | Stable   |

| 0 -          | 0              | 1              | 0              | 0               | 0   | Unstable |

| 0            | 1              | 0              | 1              | - 1             | 0 - | Unstable |

| 0            | 1,             | 1              | 1 .            | 1               | 0   | Stable   |

| 1            | 0              | 0              | 1              | 0               | 1   | Unstable |

| 1 -          | 0              | . 1            | 0 .            | 0               | 0   | Unstable |

| 1            | 1              | 0              | 1 .            | 0               | 1   | Stable   |

| 1            | 1              | 1              | 1              | 1               | 0   | Stable   |

Table 4.2 Truth table

Step 3: Plot the transition table

Figure 4.8 Transition table

The rows of transition table shown in figure 4.8 represent input 'x' and columns of transition table represent present state  $y_2y_1$ . The number written in the transition table represent next state  $Y_2Y_1$ . The circle around  $Y_2Y_1$  indicate that the state is stable.

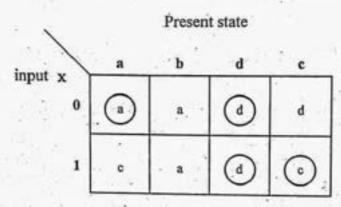

### Step 4: Assign states for the binary values and plot the state table

Here present states and next states are 00, 01, 10 and 11.So assign a=00, b=01, c=10 and d=11. The state table can be drawn as shown in figure 4.9.

Figure 4.9 State table

Step 5: Plot the output map

| 1 | a   | b | d | c |

|---|-----|---|---|---|

| 0 | 0   |   | 0 |   |

| 1 | 1.0 |   | 0 | 1 |

Figure 4.10 Output map

The output is mapped for all stable states which are indicated by circles as shown in figure 4.10. For the unstable states, the output is mapped unspecified.

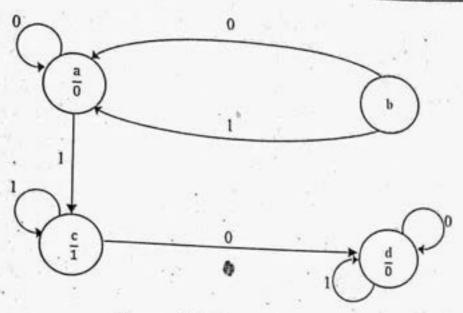

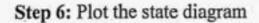

### Step 6: Plot the state diagram

By using the state table and output map, draw the next state transition for input x=0 and x=1 as shown in figure 4.11. Similarly mark the output Z from the output map for each stable state.

Figure 4.11 State diagram

Example 4.1: An asynchronous sequential circuit has two internal states and one output. The excitation and output function describing the circuit are as follows.

$$Y_1 = x_1x_2 + x_1y_2 + x_2y_1$$

$$Y_2 = x_2 + x_1y_1y_2 + x_1y_1$$

$$Z = x_2 + y_1$$

Solution:

Step 1: Since the equations are directly given proceed to step 2.

Step 2: Plot the truth table

Here  $y_2$  and  $y_1$  are present states,  $Y_2$  and  $Y_1$  are next states,  $x_2$  and  $x_1$  are inputs and Z is the output. Here the number of inputs is equal to number of present states, so we can write either inputs or present state first in the truth table as shown in table 4.3.

First write the possible binary combination for present states and inputs. Then substituting the value of  $x_2$ ,  $x_1$ ,  $y_2$ ,  $y_1$  and Z in the next state and output functions, find the next states  $Y_2$ ,  $Y_1$  and output Z. For the given input, if the next states  $Y_2$ ,  $Y_1$  is same as that of present states  $Y_2$ , then the state is said to be stable.

| In             | put | Preser         | ıt state       | Next           | state            | Output | States   |

|----------------|-----|----------------|----------------|----------------|------------------|--------|----------|

| x <sub>2</sub> | X1  | y <sub>2</sub> | y <sub>1</sub> | Y <sub>2</sub> | Y <sub>1</sub> . | Z      |          |

| 0              | 0   | 0              | 0              | 0              | 0                | 0      | Stable   |

| 0              | 0   | 0              | 1              | 0              | 0                | 1      | Unstable |

| 0              | 0   | 1              | 0              | 0              | 0                | 0      | Unstable |

| 0              | 0   | 1              | 1 -            | 0              | 0                | 1      | Unstable |

| 0              | 1   | 0              | 0              | 0              | 0.               | . 0    | Stable   |

| 0              | 1   | 0.             | 1              | 1              | 0                | 1      | Unstable |

| 0              | 1   | 1              | 0.             | 0              | 1                | 0      | Unstable |

| 0              | 1   | . 1            | 1              | 1              | 1 .              | - 1    | Stable   |

| 1              | 0   | 0-             | 0              | 9              | 0                | 1      | Unstable |

| 1              | 0   | 0              | 1 .            | 1              | 1                | 1      | Unstable |

| 1              | 0   | 1              | 0              | 1              | . 0              | 1      | Stable   |

| 1              | 0   | 1              | 1              | 1 :            | 1                | 1      | Stable   |

| 1              | 1   | 0 .            | - 0            | . 1            | 1,               | 1      | Unstable |

| 1              | 1   | 0 -            | •1             | 1              | 1                | 1      | Unstable |

| 1              | . 1 | 1              | . 0            | 1              | 1                | 1      | Unstable |

| 1              | 1   | 1              | 1              | 1              | 1                | 1      | Stable   |

Table 4. 3 Truth table

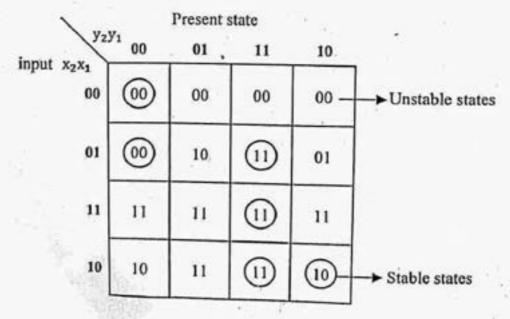

Step 3: Plot the transition table.

Figure 4.12 Transition table

Here the rows of transition table represent inputs x2x1 and columns of transition table represent present states y2y1. The number written in the table represent next state Y<sub>2</sub>Y<sub>1</sub>. The circle around Y<sub>2</sub>Y<sub>1</sub> indicates that the state is stable

Step 4: Assign states for the binary values and plot the state table

Here present states and next states are 00, 01, 10 and 11. So assign a=00, b=01, c=10 and d=11. The state table can be drawn as shown in figure 4.13.

|     | Present    | state       |                   |                                 |

|-----|------------|-------------|-------------------|---------------------------------|

| a   | b          | d           | c                 |                                 |

| a   | a          | a           | a -               | → Unstable states               |

| (a) | С          | (d)         | b .               |                                 |

| ď   | d          | (d)         | d .               |                                 |

| · c | d          | (1)         | <u></u>           | ➤ Stable states                 |

|     | (a)<br>(d) | a b a c d d | a a a a c d d d d | a b d c a a a a - a c d b d d d |

Figure 4.13 State table

Step 5: Plot the output map

| \       |     | 1.0 | Present | state |   |

|---------|-----|-----|---------|-------|---|

| input x | 2×1 | а   | ь       | d     | e |

|         | 00  | 0   |         | -     | • |

|         | 01  | 0-  |         | 1     |   |

|         | 11  |     |         | 1     |   |

|         | 10  |     |         | 1     | 1 |

Figure 4.14 Output map

The output is mapped for all stable states which are indicated by circles as shown in figure 4.14. For unstable states, the output is mapped unspecified.

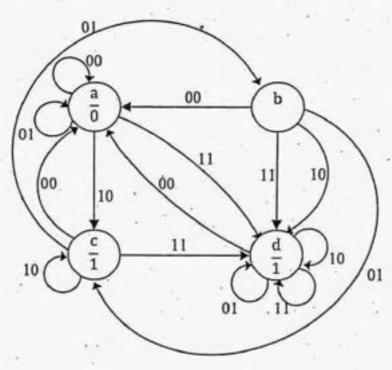

Figure 4.15 State Diagram

By using the state table, draw the next state transition for input  $x_2x_1 = 00$ ,  $x_2x_1 = 01$ ,  $x_2x_1 = 10$  and  $x_2x_1 = 11$  as shown in figure 4.15. Similarly mark the output Z from the output map for each stable state.

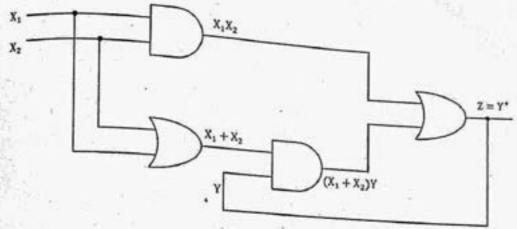

Example 4.2: An asynchronous sequential circuit is described by the following excitation and output function.

$$Y = X_1X_2 + (X_1 + X_2)Y$$

$Z=Y$

- (i) Draw the logic diagram.

- (ii) Derive the transition table and output map.

- (iii) Describe the behavior of the circuit

#### Solution:

Here Y is found on both sides of the equations.

Let the next state be  $Y^+ = X_1X_2 + (X_1 + X_2)Y$

Output  $Z = Y^+$

Here Y is the present state, Y<sup>+</sup> is the next state, Z is the output and X<sub>1</sub> and X<sub>2</sub> are the inputs.

# Logic diagram

Figure 4.16

| Present state | In             | put            | Next state     | Output | State    |

|---------------|----------------|----------------|----------------|--------|----------|

| Y             | X <sub>2</sub> | X <sub>1</sub> | Y <sup>+</sup> | Z      | State    |

| 0             | 0              | 0              | 0              | 0      | Stable   |

| 0             | 0              | 1              | . 0 .          | 0      | Stable   |

| , 0           | 1              | 0              | 0              | 0      | Stable   |

| 0             | 1              | 1              | 1 ,            | 1      | Unstable |

| 1             | 0              | 0              | 0 .            | 0      | Unstable |

| 1             | 0              | 1              | i              | 1.     | Stable   |

| 1             | 1              | 0,             | 1              | 1      | Stable   |

| 1             | 1              | 1              | 1              | 1      | Stable   |

Table 4.4 Truth table

The truth table should contain the present state (Y), inputs (X<sub>1</sub>, X<sub>2</sub>), next state (Y') and output 'Z'. Here the number of present states is less than the number of inputs, so write the present state first in the truth table as shown in table 4.4.

First write the possible binary combination for present states and inputs. Then by substituting the value of Y,  $X_1$  and  $X_2$  in the next state and output equation, find and Z. For the given input, if the next state  $Y_2Y_1$  is same as that of present states  $Y_2Y_1$ , then the state is said to be stable.

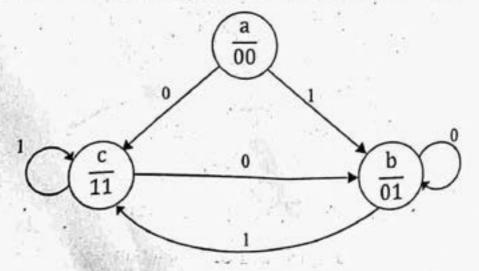

### ii. Transition table and output map

Figure 4.17 Transition table

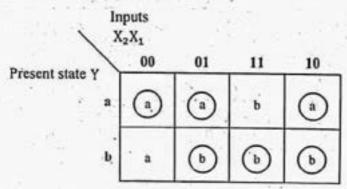

The rows of transition table represents the present state 'Y' and columns of transition table represents the inputs 'X<sub>2</sub>X<sub>1</sub>'. The number written in the table represents next state Y<sup>+</sup>. The circle around Y<sup>+</sup> indicate that the state is stable which is shown in figure 4.17. Then assign states for the binary values and plot the state table. Here present states and next states are 0 and 1. So assign a=0 and b=1. The state table can be drawn as shown in figure 4.18.

Figure 4.18 State table.

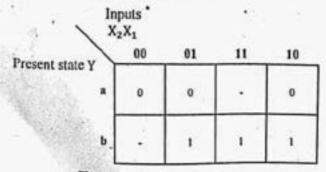

The output is mapped for all stable states which is indicated by circles. For unstable states, the output is mapped unspecified.

Figure 4.19 Output map

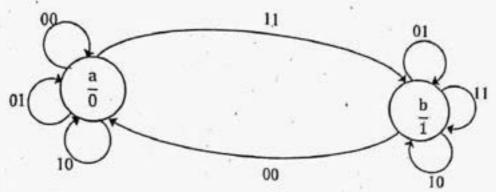

plot the state diagram by using the state table and output map as shown in figure 4.20.

Figure 4.20 State diagram

### ii. Behavior of the circuit

The given circuit gives the carry output of the full adder circuit.

### 4.3 REDUCTION OF STATE AND FLOW TABLES

| Present state | Next state, Output Z |         |         |         |  |  |  |

|---------------|----------------------|---------|---------|---------|--|--|--|

|               | xy = 00              | xy = 01 | xy = 11 | xy = 10 |  |  |  |

| a             | (a), 0               | b,-     | -,-     | с,-     |  |  |  |

| ь             | a,-                  | (b), 0  | d,-     | -,-     |  |  |  |

| c             | a,-                  | -3-     | е,-     | ©, 0    |  |  |  |

| . d           | 7.7                  | f,-     | d, 1    | c,-     |  |  |  |

| e             | -,-                  | f,-     | (e), 0  | c,-     |  |  |  |

| f             | a,-                  | (f), 1  | d,-     | -,-     |  |  |  |

Table 4.5 Primitive flow table.

Consider a primitive flow table shown in table 4.5

The number of states in the primitive flow table can be reduced by using state reduction technique. This is similar to state reduction in synchronous sequential circuits. State reduction is nothing but reducing the equivalent states to a single state. Two states are said to be equivalent if the two states produces the same next state and same output for each input. Here a, b, c, d, e, and f are present states.

Two rows of primitive flow table can be merged into a single row, if there is no output conflict and no state conflicts in any column.

A stable state and unstable state can be merged to a stable state. The specified output is filled when specified output is merged with unspecified output.

In the primitive flow table shown in table 4.6 states a and b have same next states and outputs so this states can be merged as shown below.

|         | Present state | Next state, Output Z |         |         |         |  |

|---------|---------------|----------------------|---------|---------|---------|--|

|         |               | xy = 00              | xy = 01 | xy = 11 | xy = 10 |  |

|         | a             | a), 0                | b,-     | -,-     | с,-     |  |

|         | ь             | a,-                  | (b), 0  | d,-     | -,-     |  |

| Reduced | · •           | <b>+</b>             | •       | +       | +       |  |

| state   | So            | (a), 0               | (b), 0  | · d,-   | c       |  |

Table 4.6

Here states a and b are reduced to a single state So.

$$(a,b) \rightarrow S_0$$

Here the next state of 'a' when xy = 00 is 'a' and it is stable but the next state of 'b' when xy = 00 is 'a' and it is unstable. So the reduced state is 'a' and it is

The next state of 'a' when xy = 11 is unspecified, but the next state of 'b' when xy = 11 is 'd' and it is unstable. So the reduced state is 'd' and it is unstable.

The output of state 'a' when xy=00 is 0 and the output of state 'b' when xy=00 is unspecified. So the reduced output is 0.

The output of state 'a' and 'b' when xy=11 is unspecified so the reduced output is also unspecified.

|   |   |         | Next state, Output Z |         |         |  |  |  |  |

|---|---|---------|----------------------|---------|---------|--|--|--|--|

| 1 |   | xy = 00 | xy = 01.             | xy = 11 | xy = 10 |  |  |  |  |

|   | с | · a ,-  | .,                   | e,-     | (0), 0  |  |  |  |  |

|   | e | -,-     | f ,÷                 | (e), 0  | c,-     |  |  |  |  |

Table 4.7

In the primitive flow table state 'c' and 'e' have same next states and outputs. So these states can be merged to S1.

$$(c, e) \rightarrow S_1$$

Also the states 'd' and 'f' have same next states and outputs. So 'd' and 'f' can be merged to S2

$$(d, f) \rightarrow S_2$$

|         | Present state |         | Next s  | tate, Output |         |

|---------|---------------|---------|---------|--------------|---------|

|         | Trosent surv  | xy = 00 | xy = 01 | xy = 11      | xy = 10 |

|         | d             | - ;-    | f,-     | (d), 1       | с,-     |

|         | f             | a,-     | f),1    | , d , -      | 1       |

| ducéd r |               |         | (f), 1  | (d), 1       | с,-     |

Table 4.8

| Present state  | 1 5.0   | Next st | tate, Output Z |         |

|----------------|---------|---------|----------------|---------|

|                | xy = 00 | xy = 01 | xy = 11        | xy = 10 |

| S <sub>0</sub> | a), 0   | (b), 0  | d , -          | с,-     |

| Si             | a ,-    | f ,-    | 0,0            | ©, 0    |

| S2             | a ,-    | (f), 1  | (d), 1         | c ,-    |

Table 4.9 Reduced flow table

Two states can be reduced to a single state as given in table 4.10.

| Equivalent state                          | Reduced state      |

|-------------------------------------------|--------------------|

| Stable state and unstable state           | Stable state       |

| Stable state and stable state             | Stable state       |

| Stable state and unspecified state        | Stable state       |

| Unstable state and unstable state         | Unstable state     |

| Unstable state and unspecified state      | Unstable state     |

| Specified output and unspecified output   | Specified output   |

| Specified output and specified output     | Specified output   |

| Unspecified output and unspecified output | Unspecified output |

Table 4.10

### 4.4 RACE FREE STATE ASSIGNMENT

To avoid critical races, it is necessary that present state and next state should be given adjacent assignments. If the present state and next state are said to be adjacent, if the binary value differ in only one bit. For example 010 and 011 are adjacent because they differ only in the third bit. The binary values 010 and 111 are not adjacent because the first and third bit differs. Consider the reduced state table shown in table 4.11.

| Present state    |                   | Next sta             | ite, output Z        |                      |

|------------------|-------------------|----------------------|----------------------|----------------------|

|                  | xy = 00           | xy = 01              | xy = 11              | xy = 10              |

| So               | $(S_0)$ , 0       | (S <sub>0</sub> ), 0 | S <sub>2</sub> ,-    | S <sub>1</sub> ,-    |

| . S <sub>1</sub> | S <sub>0</sub> ,- | S <sub>2</sub> ,-    | (S <sub>1</sub> ), 0 | (S <sub>1</sub> ), 0 |

| S <sub>2</sub>   | S <sub>0</sub> ,- | $(S_2)$ , 1          | (S <sub>2</sub> ), 1 | S <sub>1</sub> ,-    |

Table 4.11

Now if we assign  $S_0 = 00$ ,  $S_1 = 01$  and  $S_2 = 10$

| Present state       | Next state A+B+, Output Z |         |         |         |  |

|---------------------|---------------------------|---------|---------|---------|--|

|                     | xy = 00                   | xy = 01 | xy = 11 | xy = 10 |  |

| S <sub>0</sub> (00) | 00,0                      | 00,0    | 10,-    | 01,-    |  |

| S <sub>1</sub> (01) | 00,-                      | 10,-    | 01,0    | 01,0    |  |

| S <sub>2</sub> (10) | 00,-                      | 10 , 1  | 10,1    | 01,-    |  |

Table 4.12 State assignment without race free

Here if the present state is AB=01 and input is xy=01, the next state is  $^{A^+B^+}$  = 10. Also if the present state is AB=10 and input is 10, the next state  $^{A^+B^+}$  = 01. In both cases present state and next state are not adjacent. A race-free assignment can be obtained if we add an extra row to the flow table. The first three represent the same conditions as the original three- row table. The fourth row is assigned with 11. Now the transition of 01 to 10 for input xy=01 must go through 11. Also the transition of 10 to 01 for input xy=10 must go through 11.

| Present             | 1       | Next state / | A+B+, outp | ut      |

|---------------------|---------|--------------|------------|---------|

| state ·             | xy = 00 | xy = 01      | xy = 11    | xy = 10 |

| S <sub>0</sub> (00) | 00,0    | 00,0         | 10,-       | 01,-    |

| S <sub>1</sub> (01) | 00,-    | 11,-         | 01,0       | 01,0    |

| S <sub>2</sub> (10) | 00,-    | 10,1         | 10,1       | 11,-    |

| S <sub>3</sub> (11) | -,-     | 10,-         | -,-        | 01, -   |

Table 4.13 Race Free State assignment

Since the present states and next states differ by single bit, the circuit for this flow table will be free from races.

#### 4.5 INCOMPLETELY SPECIFIED STATE MACHINES

Sequential circuits in which some of the states are left unspecified are called Incompletely specified state machines. In sequential circuits, not all combinations of states and inputs are possible. For example, consider the state table shown in table 4.14. Here the state 'b' will never receive a '0' input and hence the next state and outputs are left unspecified by a dash (-). In some situation, the state transitions are completely defined but for some combinations of states and inputs, the output values may be left unspecified.

| Present state | Next state | , Output |

|---------------|------------|----------|

| * I I I I     | X = 0      | X = 1    |

| a             | d,1        | b,0      |

| ь             | ,-         | c,0      |

| c             | a, 1       | ·b,-     |

| d             | a, 0       | d,1      |

Table 4.14 State table

In the state table shown in table 4.14, the next state of 'c' is specified as 'b' for the input '1' but the output is unspecified as dash. When a state transition is unspecified, the future behavior of the sequential machine may become unpredictable.

# 4.6 DESIGN OF ASYNCHRONOUS SEQUENTIAL CIRCUITS

The procedure for designing asynchronous sequential circuit is given below.

- 1. From the given description, draw the state diagram.

- 2. Construct a primitive flow table from the state diagram.

- Reduce the primitive flow table by eliminating the redundant states by using state reduction.

- 4. Assign binary values to states based on race free state assignment.

- 5. Find output table by using a flip-flop excitation table.

- 6. Find the flip-flop input equations and output equations using K-map.

- 7. Draw the logic diagram.

Example 4.3: Design an asynchronous sequential circuit with two inputs X and Y with one output Z. Whenever Y is 1, input X is transferred to Z. When Y is 0, the output does not change for any change in X. Use D flip-flop.

Solution: It is given that X and Y are inputs and Z is the output.

If Y=0, there will be no change in output

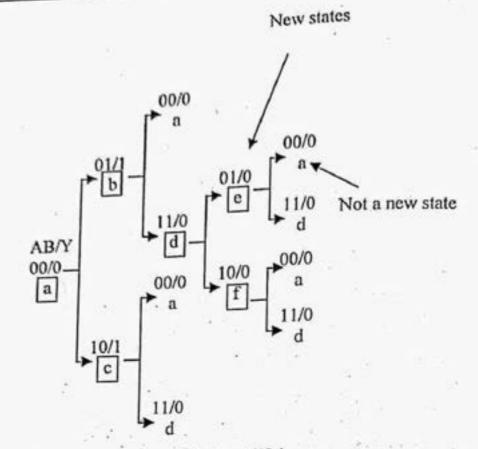

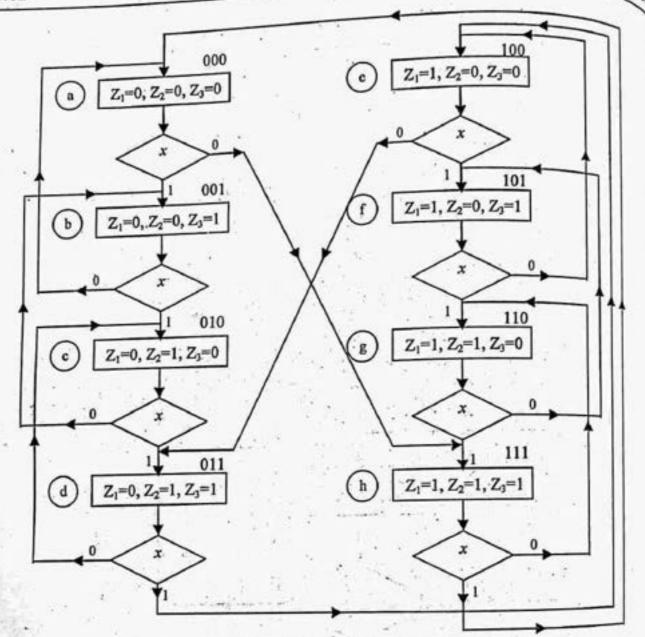

Step 1: Draw the state diagram.

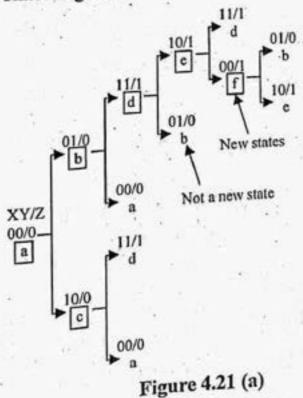

The state diagram for the given problem can be easily drawn using the diagram shown in figure 4.21(a). Initially assume XY=00 and Z=0. The input XY=00 can change to XY=01 or XY=10. Given that if Y=1, Z=X. If Y=0, the output does not change.

Therefore XY=01 has the output Z=0 and XY=10 has the output Z=0. Assign 01/0 as 'b', 10/0 as 'c'. Highlight a, b and c because a, b and c are new states. The input XY=01 can change to XY=11 or XY=00. The output when XY=11 is 1 and XY=00 is 0. Assign 11/1 as 'd' and highlight it because it is a new state.

Assign 00/0 as 'a' because we have already assigned 00/0 as 'a'. No need to highlight it because it is not a new state. The input XY=10 can change to XY=11 or XY=00. The output when XY=11 is 1 and XY=00 is 0. Assign 11/1 as'd' and 00/0 as 'a'. No need to highlight 'a' and 'd' because 'a' and 'd' are not a new states. Proceed this process for all new states.

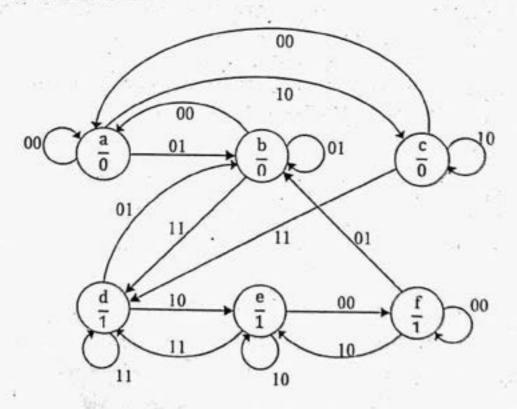

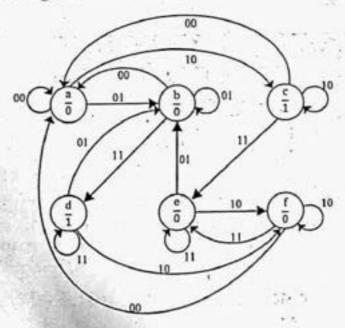

Now the state diagram can be easily drawn using figure 4.21(a). The different states are a, b, c, d, e and f.

Figure 4.21 (b) State diagram

Step 2: Construct the primitive flow table

| Present state | Next state, Output Z |        |        |       |  |

|---------------|----------------------|--------|--------|-------|--|

|               |                      | XY=01  |        | XY=10 |  |

| a             | a, 0                 | b,-    | -,-    | c,-   |  |

| Ъ             | a,-                  | (b), 0 | d,-    | -,-   |  |

| С             | a,-                  | -,-    | ' d,-  | (0,0  |  |

| d             | -,-                  | b,-    | (d), 1 | e,-   |  |

| e             | f,-                  | -,-    | d,-    | @1    |  |

| f             | ① i                  | b,-    | -,-    | 'e,-  |  |

Table 4.15 Primitive flow table

Here the circle represents that the state is stable.

Step 3: Reduce the primitive flow table

The primitive flow table can be minimized by merging the states a, b, c to a single state 'S<sub>0</sub>' because the next state and the output for the states a, b, c are same.

$$(a, b, c) \rightarrow S_0$$

Also we can merge the states d, e, f to a single state 'S<sub>1</sub>' because the next state and the output for the states d, e, f are same.

$$(d, e, f) \rightarrow S_1$$

| Present state  |        | Next state         | , Output Z | 9                     |

|----------------|--------|--------------------|------------|-----------------------|

| *              | XY=00  | XY=01              | XY=11      | XY=10                 |

| S <sub>0</sub> | §₀, 0  | S <sub>0</sub> , 0 | S1,-       | .(S <sub>0</sub> ), 0 |

| Sı             | (S), 1 | So,-               | (S), 1     | <b>(S)</b> , 1        |

Table 4.16 Reduced primitive flow table

Step 4: Assign binary values to states based on race free state assignment.

Here, there are two states  $S_0$  and  $S_1$ . So assign  $S_0$ =0,  $S_1$ =1 also, let the present state be A and the Next state be A<sup>+</sup>. Let the output be Z. Since the present states and hext states differ by single bit, the circuit for this flow table will be free from races.

|               | N.     | ext state A | +, Output | t Z   |

|---------------|--------|-------------|-----------|-------|

| Present state | 777-00 | xy=01       | XY=11     | XY=10 |

| A             | XY=00  | 0.0         | 1,-       | 0,0   |

| 0             | 0,0    | 0 -         | 1,1       | 1,1   |

| . 1           | 1,1    | 0,          |           |       |

Table 4.17 State assignment

Step 5: Find the output table.

By using the excitation table of D flip-flop shown in table 4.18, draw the output table.

| A | A+ | $\mathbf{D}_{\mathbf{A}}$ |

|---|----|---------------------------|

| 0 | 0  | . 0                       |

| 0 | 1. | 1                         |

| 1 | 0  | 0                         |

| 1 | 1  | 1                         |

Table 4.18 Excitation table of D flip-flop

| Present state | Flip-flop input DA, Output Z |       |       |       |

|---------------|------------------------------|-------|-------|-------|

|               | XY=00                        | XY=01 | XY=11 | XY=10 |

| 0             | 0,0                          | 0,0   | 1,-   | 0,0   |

| . 1           | 1,1                          | 0,-   | 1,1   | 1,1   |

Table 4.19 Output table

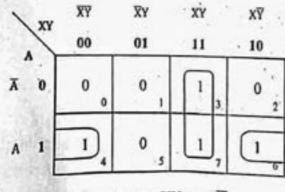

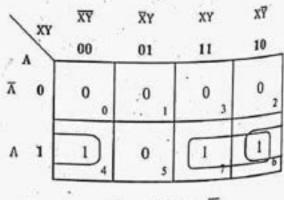

Step 6: Find the flip-flop input equations and output equations using K-map. Assume '0' for unspecified outputs.

### K-map for DA

$D_A = XY + A\overline{Y}$

### K-map for Z

$Z = AX + A\overline{Y}$

511p 7: Draw the logic diagram

Figure 4.22 Logic diagram

Example 4.4: Design an asynchronous sequential circuit that has two inputs  $x_1$  and  $x_2$  and one output Z. The output Z=1, if  $x_1$  changes from 0 to 1. Z=0, if  $x_2$  changes from 0 to 1 and Z=0 otherwise. Realize the circuit using JK flip-flop.

### Solution:

It is given that  $x_1$  and  $x_2$  are inputs and Z is the output.

If x1 changes from 0 to 1, Z=1

If x2 changes from 0 to 1, Z=0

Otherwise, Z=0

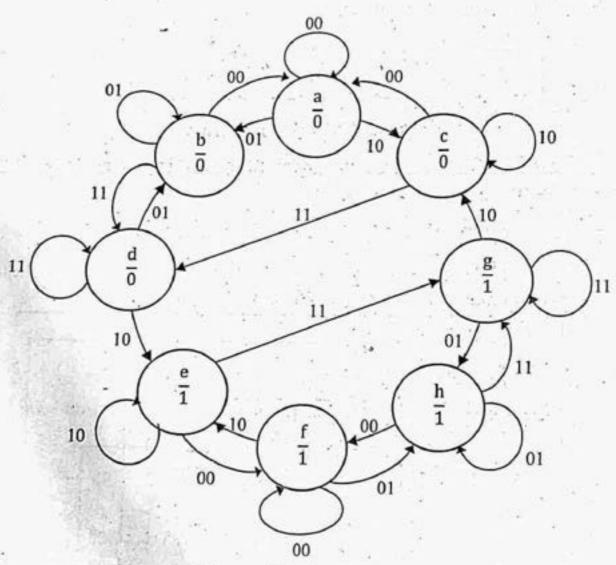

# Step 1: Draw the state diagram

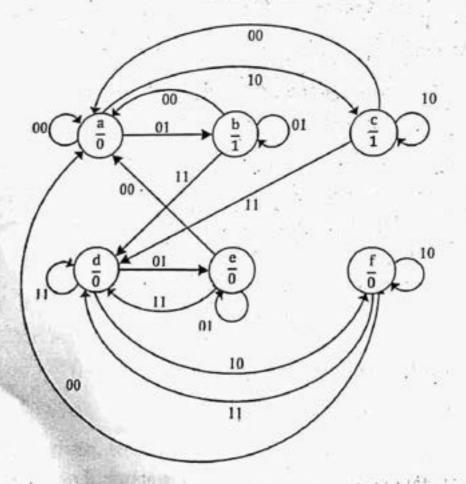

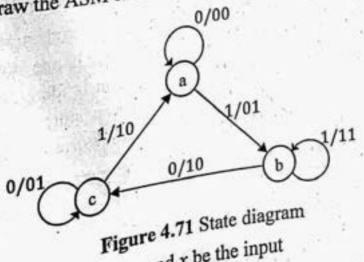

The state diagram for the given problem can be easily drawn using the diagram shown in figure 4.23.

Figure 4.23

Initially assume  $x_1x_2=00$  and output Z=0. The input  $x_1x_2=00$  can change to  $x_1x_2=01$  or  $x_1x_2=10$ . If  $x_2$  changes from 0 to 1, Z=0. If  $x_1$  changes from 0 to 1, Z=1. So the next states of 00/0 are 01/0 and 10/1. Assign 00/0 as 'a', 01/0 as 'b' and 10/1 as 'c'. Highlight a, b, and c because a, b and c are new states. Proceed this process for all new states.

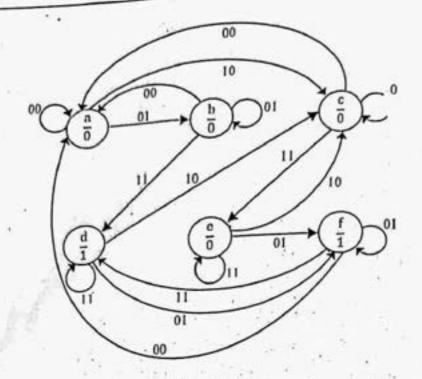

Now the state diagram can be easily drawn from the figure 4.23.

Figure 4.24 State diagram

Step 2: Construct the primitive flow table.

| Present state | Next state, Output Z |                |                |                                   |

|---------------|----------------------|----------------|----------------|-----------------------------------|

|               | $x_1 x_2 = 00$       | $x_1 x_2 = 01$ | $x_1 x_2 = 11$ | x <sub>1</sub> x <sub>2</sub> =10 |

| a             | (a), 0               | b,-            |                |                                   |

| ь,            | a,-                  | (b), o         | d,-            | c,-                               |

| c             | a,-                  | 7,7            | e,-            | ©1                                |

| d             | -,-                  | b,-            | @1             | f,-                               |

| e             | -,-                  | b,-            | @0             | f,-                               |

| f ·           | a,-                  | -,-            | e,-            | ① O                               |

Table 4.20 Primitive flow table

### Step 3: Reduce the primitive flow table

The primitive flow table can be minimized by merging the states 'a' and 'c' to a single state So

$$(a, c) \rightarrow S_0$$

Also we can merge the states 'b' and 'd' to a single state 'S1'

$$(b, d) \rightarrow S_1$$

Also we can merge the states 'e' and 'f' to a single state 'S2'

$$(e, f) \rightarrow S_2$$

| Present state  | 1700                              | Next state        | , Output Z        |                   |

|----------------|-----------------------------------|-------------------|-------------------|-------------------|

|                | x <sub>1</sub> x <sub>2</sub> =00 | $x_1 x_2 = 01$    | $x_1 x_2 = 11$    | $x_1 x_2 = 10$    |

| So             | S <sub>0</sub> , 0                | S <sub>1</sub> ,- | S <sub>2</sub> ,- | <b>S</b> , 1      |

| S <sub>1</sub> | S <sub>0</sub> ,-                 | (S), 0            | (S), 1            | S <sub>2</sub> ,- |

| S <sub>2</sub> | So,-                              | S <sub>1</sub> ,- | §3, 0             | (S), 0            |

Table 4.21 Reduced primitive flow table

Step 4: Assign binary values to the states based on race free state assignment.

Since there are three states assign S<sub>0</sub>=00, S<sub>1</sub>=01, S<sub>2</sub>=10. Let the present states be AB and the next state be A+B+.

| Present state | Next state A+B+, Output Z         |                                   |                |                |

|---------------|-----------------------------------|-----------------------------------|----------------|----------------|

| AB            | x <sub>1</sub> x <sub>2</sub> =00 | x <sub>1</sub> x <sub>2</sub> =01 | $x_1 x_2 = 11$ | $x_1 x_2 = 10$ |

| 00            | 00,0                              | 01,-                              | 10,-           | 00,1           |

| 01            | 00,-                              | 01,0                              | 01,1           | 10,-           |

| 10            | 00,-                              | 01,-                              | 10,0           | 10,0           |

Table 4.22 State assignment

Here the present state AB=10 and the next state A+B+ = 01 differs by two bits.

Also the present state AB=01 and the next state A+B+ = 10 differs by two bits. Since the present state and next states are not adjacent, races will be there for the circuit of the above flow table. So by race free state assignment the above flow table can be modified by a new state 11.

| Present state | Next state A+B+, Output Z         |                                   |                |                |

|---------------|-----------------------------------|-----------------------------------|----------------|----------------|

| AB            | x <sub>1</sub> x <sub>2</sub> =00 | x <sub>1</sub> x <sub>2</sub> =01 | $x_1 x_2 = 11$ | $x_1 x_2 = 10$ |

| 00            | 00,0                              | 01,-                              | 10.,-          | 00,1           |

| 01            | 00,                               | 01,0                              | 01,1           | 11,-           |

| . 10          | 00,-                              | 11,-                              | 10,0           | 10,0           |

| 11            | -;-                               | 01,-                              | -,-            | 10,-           |

Table 4.23 Race free state assignment

Step 5: Find the output table.

By using the excitation table of JK flip-flop shown in table 4.24, draw the output table.

| A   | A <sup>+</sup> | $J_A$ | $K_{\Lambda}$ |

|-----|----------------|-------|---------------|

| . 0 | 0              | 0     | X             |

| 0   | 1              | 1     | X             |

| 1   | 0              | X     | 1             |

| - 1 | 1              | Χ.    | 0             |

Table 4.24 Excitation table of JK flip-flop

| Present state | Flip-flop                         | inputs JA l                       | $K_A$ , $J_B K_B$ , | Output Z    |

|---------------|-----------------------------------|-----------------------------------|---------------------|-------------|

| AB            | x <sub>1</sub> x <sub>2</sub> =00 | x <sub>1</sub> x <sub>2</sub> =01 | $x_1x_2=11$         | $x_1x_2=10$ |

| 00            | 0X,0X,0                           | 0X,1X,-                           | 1X,0X,-             | 0X,0X,1     |

| 01            | 0X,X1,-                           | 0X,X0,0                           | 0X,X0,1             | 1X,X0,-     |

| 10            | X1,0X,-                           | X0,1X,-                           | X0,0X,0             | X0,0X,0     |

| 11            |                                   | X1,X0,-                           | -,-,-               | X0,X1,      |

Table 4.25 Output table

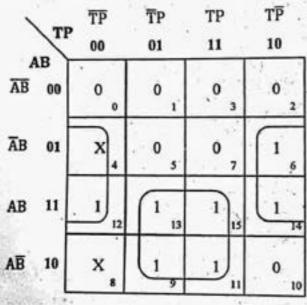

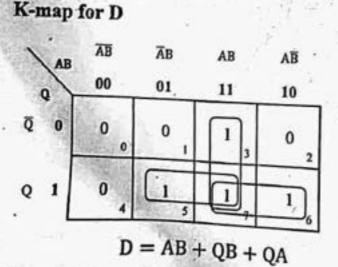

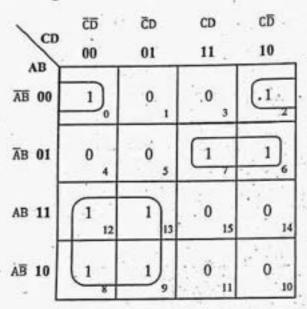

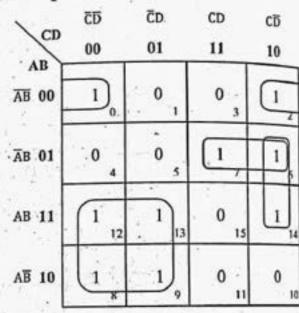

Step 6: Find the flip-flop input equations and output equations using K-map.

| -map fo | $\vec{x}_1\vec{x}_2$ | $\bar{x}_1 x_2$ | , x <sub>1</sub> x <sub>2</sub> | $x_1 \vec{x}_2$ |

|---------|----------------------|-----------------|---------------------------------|-----------------|

| 12123   | 00                   | 01              | 11                              | 10              |

| AB 00   | 0 0                  | 0               |                                 | 0 2             |

| ĀB 01   | 0 4                  | 0 5             | 0 7                             | 1 6             |

| AB 11   | 0 12                 | X<br>13         | 0                               | ×,              |

| AB 10   | X                    | x,              | X                               | X               |

$J_{A} = \overline{B}x_{1}x_{2} + Bx_{1}\overline{x}_{2}$

### K-map for JB

| \x1.x2 | $\bar{x}_1\bar{x}_2$ | ₹ <sub>1</sub> x <sub>2</sub><br>01 | x <sub>1</sub> x <sub>2</sub> | x <sub>1</sub> x̄ <sub>2</sub> |

|--------|----------------------|-------------------------------------|-------------------------------|--------------------------------|

| AB 00  | 0 0                  | 1                                   | 0 3                           | 0 2                            |

| ĀB 01  | X <sub>4</sub>       | X                                   | Х,                            | X 6                            |

| AB 11  | 0 .                  | X 13                                | 0 15                          | X 14                           |

| Æ 10   | 0 8                  | 1,                                  | 0                             | 0 10                           |

## $J_B = \overline{x}_1 x_2$

# K-map for KA

| 1       | x1 x2   | $\vec{x}_1 \vec{x}_2$ | ₹ <sub>1</sub> x <sub>2</sub><br>01 | 11   | x <sub>1</sub> x̄ <sub>2</sub> |

|---------|---------|-----------------------|-------------------------------------|------|--------------------------------|

| A<br>AB | B<br>00 | X,                    | X 1                                 | . X  | X 2                            |

| ÃΒ      | 01      | X 4                   | X                                   | X ,  | X 6                            |

| AB      | 11      | 0 12                  | 1                                   | 0 15 | 0 14                           |

| ΑB      | 10      | 1                     | 0 9                                 | 0 11 | 0 ~ 10                         |

$$K_{A} = \overline{B}\overline{x}_{1}\overline{x}_{2} + B\overline{x}_{1}x_{2}$$

## K-map for KB

| )    | $\bar{x}_1\bar{x}_2$ $00$ | x̄₁x₂<br>01 | x <sub>1</sub> x <sub>2</sub> | 10             |

|------|---------------------------|-------------|-------------------------------|----------------|

| AB 0 | 0 X                       | X           | · X,                          | X <sub>2</sub> |

| ⊼в 0 | 1 1                       | 0           | 0 7                           | 0 6            |

| AB 1 | 1 0                       | 0 13        | 0 15                          | 1 14           |

| AB 1 | 0 X                       | X ,         | X                             | X 10           |

$$\mathbf{K}_{\mathrm{B}} = \overline{\mathbf{A}} \overline{\mathbf{x}}_{1} \overline{\mathbf{x}}_{2} + \mathbf{A} \mathbf{x}_{1} \overline{\mathbf{x}}_{2}$$

K-map for Z

| r Z   | ₹ <sub>1</sub> ₹ <sub>2</sub><br>1 <sup>×2</sup> 00 | £1x2<br>01 | x <sub>1</sub> x <sub>2</sub> | 10   |

|-------|-----------------------------------------------------|------------|-------------------------------|------|

| VB 00 |                                                     | 0          | 0 3                           | 0,   |

| ĀB 01 | 0 4                                                 | 0 5        | ①,                            | 0 6  |

| AB 11 | 0 12                                                | 0 13       | 0 15                          | 0 14 |

| AB 10 | 0 8                                                 | 0 9        | 0                             | 0 10 |

$$Z = \overline{AB}x_1\overline{x}_2 + \overline{A}Bx_1\overline{x}_2$$

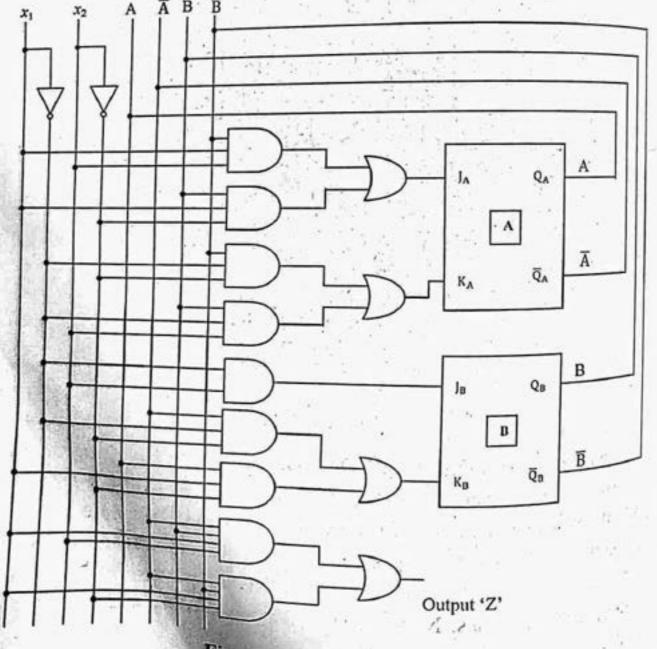

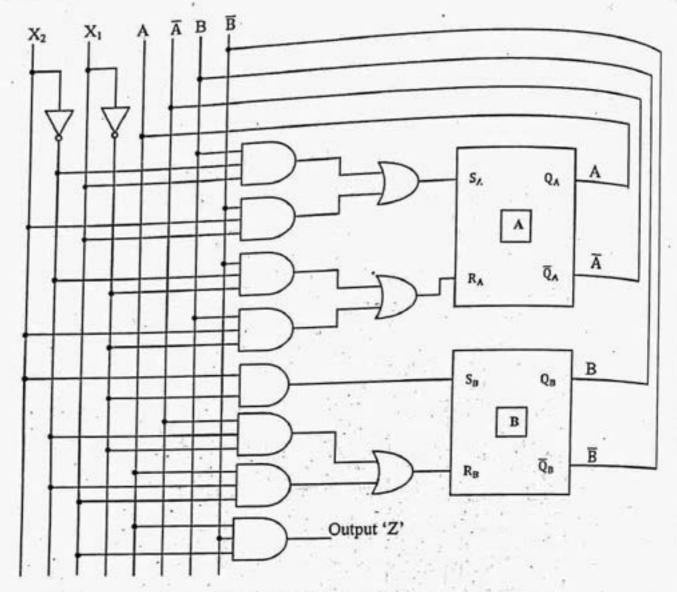

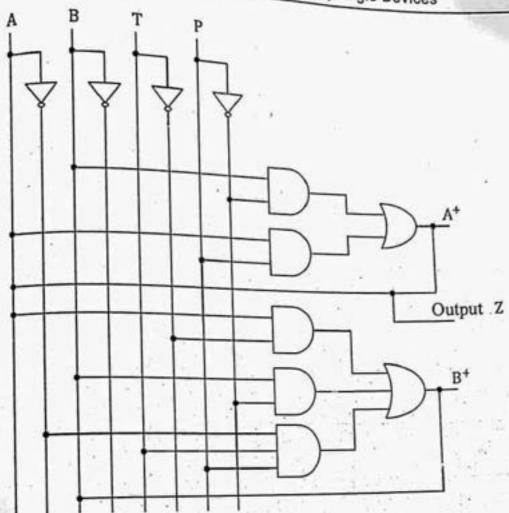

Step 7: Draw the logic diagram

Figure 4.25 Logic 4

Example 4.5: Design an asynchronous sequential circuit that has two inputs  $X_2$ and  $X_1$  and output Z. When  $X_1 = 0$ , the output Z = 0, the first change in  $X_2$  that occur while  $X_1$  is 1 will cause output Z to be 1. The output Z will remain 1 until X1 returns to 0. Use SR flip-flop.

Solution: It is given that X2, X1 are the inputs and Z is the output

If X1=0, Z=0

If there is change in X2 while X1=1, Z=1

Otherwise, Z=0

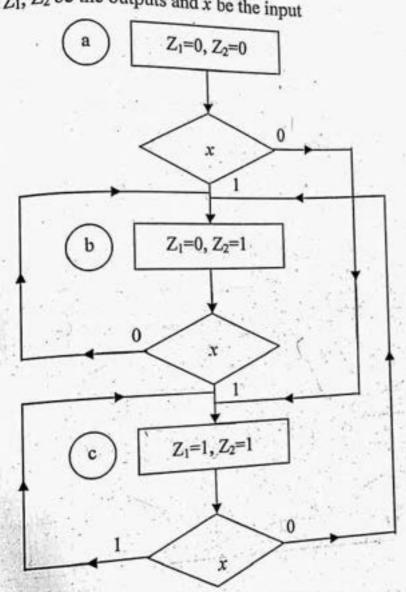

Step 1: Draw the state diagram

4.26.

The state diagram can be easily drawn by using the diagram shown in figure

Figure 4.26

Initially assume  $X_2X_1=00$  and Z=0. The input  $X_2X_1$  can change to  $X_2X_1=01$ or  $X_2X_1=10$ . It is given that if  $X_1=0$  the output is 0. If  $X_1=1$  and  $X_2$  changes then Z=1and Z=0 otherwise. So the next states of 00/0 are 01/0 and 10/0. Also assign 00/0 as 'a', 01/0 as 'b' and 10/0 as 'c'. Highlight a, b and c because a, b and c are new states. Then find the next state of 'b' and 'c'. Proceed the same process for all new states by highlighting the new states. Now the state diagram can be easily drawn from the figure 4.26.

Figure 4.27 State diagram

Step 2: Construct the primitive flow table.

| Present state |                                   | Next state, Output Z              |                                   |                                   |  |  |

|---------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|--|--|

|               | X <sub>2</sub> X <sub>1</sub> =00 | X <sub>2</sub> X <sub>1</sub> =01 | X <sub>2</sub> X <sub>1</sub> =11 | X <sub>2</sub> X <sub>1</sub> =10 |  |  |

| а             | (a), 0                            | b,-                               | -,-                               | с,-                               |  |  |

| b             | a,-                               | <b>(b)</b> , 0                    | d,-                               | 55                                |  |  |

| c             | a,-                               | 3.7                               | е,-                               | ©,0                               |  |  |

| · · d .       | ,-                                | f,-                               | (d), 1                            | c,-                               |  |  |

| e             | , - · · ·                         | f,-                               | @, 0                              | c,-                               |  |  |

| f             | a,-                               | (f), 1                            | d,-                               | -,-                               |  |  |

Table 4.26 Primitive flow table

Step 3: Reduce the primitive flow table

The primitive flow table can be minimized by merging the states 'a' and 'b' to a single state 'So'

$$(a, b) \rightarrow S_0$$

Also we can merge the states 'c' and 'e' to a single state 'S1'

$$(c, e) \rightarrow S_1$$

Also we can merge the states 'd' and 'f' to a single state 'S2'  $(d, f) \rightarrow S_2$

| Present state  |                                   | Next state                        | , Output Z                        |                                   |

|----------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

|                | X <sub>2</sub> X <sub>1</sub> =00 | X <sub>2</sub> X <sub>1</sub> =01 | X <sub>2</sub> X <sub>1</sub> =11 | X <sub>2</sub> X <sub>1</sub> =10 |

| S <sub>0</sub> | S), 0                             | <b>S</b> <sub>0</sub> , 0         | S <sub>2</sub> ,-                 | S <sub>1</sub> ,-                 |

| $S_1$          | S <sub>0</sub> ,-                 | . S <sub>2</sub> ,-               | (S), 0                            | (S), 0                            |

| S <sub>2</sub> | So ,-                             | (S), 1                            | (S), 1                            | S <sub>1</sub> ,-                 |

Table 4.27 Reduced primitive flow table

Step 4: Assign binary values to the states based on race free state assignment. Since there are three states assign,  $S_0=00$ ,  $S_1=01$  and  $S_2=10$ .

| Present state | Next state A+B+, Output Z         |                                   |                                   |                                   |

|---------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| AB            | X <sub>2</sub> X <sub>1</sub> =00 | X <sub>2</sub> X <sub>1</sub> =01 | X <sub>2</sub> X <sub>1</sub> =11 | X <sub>2</sub> X <sub>1</sub> =10 |

| 00            | 00,0                              | 00,0                              | 10,-                              | 01,-                              |

| 01            | 00,-                              | 10,-                              | 01,0                              | 01,0                              |

| 10            | 00,-                              | 10,1                              | 10,1                              | 01,-                              |

Table 4.28 State assignment

Since the states  $S_0$ ,  $S_1$ ,  $S_2$  are two bits. Let the present states are AB and the text states are  $A^+B^+$ .

Here the present state AB=10 and the next state A<sup>+</sup>B<sup>+</sup> = 01 differs by two bits. Also the present state AB=01 and the next state A<sup>+</sup>B<sup>+</sup> = 10 differs by two bits. Since the present state and next states are not adjacent races will be there for the circuit of the above flow table. So by race free state assignment the above flow table can be modified by a new state 11, which avoids the critical races.

| Present state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | B <sup>+</sup> , Output 2         | V V.=10        |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|----------------|----------|

| THE REPORT OF THE PARTY OF THE | X <sub>2</sub> X <sub>1</sub> =00 | X <sub>2</sub> X <sub>1</sub> =01 | $X_2 X_1 = 11$ | A2 A1-10 |

| AB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Section 1                         | 00,0                              | 10,-           | 01,-     |

| 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00,0                              | 11,                               | 01,0           | 01,0     |

| 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00,-                              | 10,1                              | 10,1           | 11,-     |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00,-                              | 10,-                              | -,-            | 01,-     |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -,-                               | 10,                               |                |          |

Table 4.29 Race free state assignment

Step 5: Find the output table.

By using the excitation table of SR flip-flop shown in table 4.30, draw the

output table

| A | A <sup>+</sup> | $S_{\Lambda}$ | $R_{A}$ |

|---|----------------|---------------|---------|

| 0 | 0              | 0             | X       |

| 0 | 1              | 1             | 0       |

| 1 | 0              | 0             | . 1.    |

| 1 | 1              | X             | 0       |

Table 4.30 Excitation table of SR flip-flop

| Present state | Flip-flop inputs SA RA, SB RB, Output Z |                                   |                                   |                                   |  |

|---------------|-----------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|--|

| AB            | X <sub>2</sub> X <sub>1</sub> =00       | X <sub>2</sub> X <sub>1</sub> =01 | X <sub>2</sub> X <sub>1</sub> =11 | X <sub>2</sub> X <sub>1</sub> =10 |  |

| 00            | 0X,0X,0                                 | 0X,0X,0                           | 10,0X,-                           | 0X,10,-                           |  |

| 01            | 0X,01,-                                 | 10,X0,-                           | 0X,X0,0                           | 0X,X0,0                           |  |

| . 10          | 01,0X,-                                 | X0,0X,1                           | X0,0X,1                           | X0,10,-                           |  |

| -11           | 555                                     | X0,01,-                           | -, -, -                           | 01,X0,-                           |  |

Table 4.31 Output table

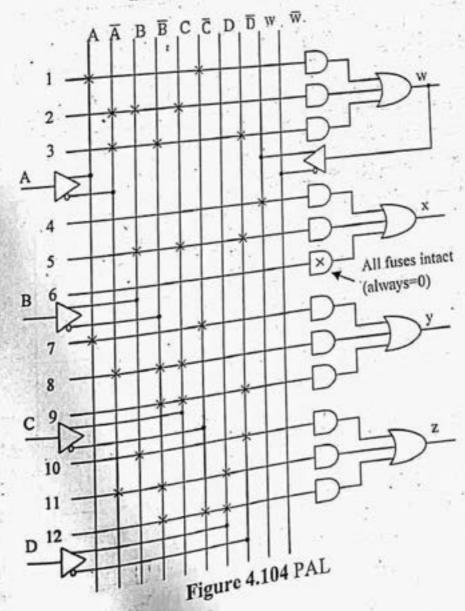

Step 6: Find the flip-flop input equations and output equations using K-map. Assume '0' for unspecified flip-flop inputs and unspecified outputs.

### K-map for RA

| X₂X₁<br>00 | ₹ <sub>2</sub> X <sub>1</sub> | X <sub>2</sub> X <sub>1</sub>                         | X <sub>2</sub> X <sub>1</sub> |

|------------|-------------------------------|-------------------------------------------------------|-------------------------------|

| x          | X                             | 0                                                     | X                             |

| X 4        | 0 5                           | X ,                                                   | X                             |

| 0 12       | 0 13                          | 0                                                     |                               |

| 1 8        | 0 ,                           | 0 11                                                  | 0                             |

|            | x 4 0                         | X 0 1 X 1 X 0 5 X 1 X 1 X 1 X 1 X 1 X 1 X 1 X 1 X 1 X | 1 00 01 11                    |

| for SB | $\vec{\chi}_2\vec{\chi}_1$ | $\overline{X}_2X_1$ | X <sub>2</sub> X <sub>1</sub> | $X_2\overline{X}_1$ |

|--------|----------------------------|---------------------|-------------------------------|---------------------|

| X27    | 00                         | 01                  | 11                            | 10                  |

| AB 00  | 0 0                        | 0                   | 0 3                           | 1 2                 |

| ÃB 01  | 0 4                        | X .                 | , X ,                         | · X                 |

| AB 11  | 0                          | 0                   | 0                             | X 14                |

| AB 10  | 0 8                        | 0 9                 | 0                             | 1                   |

$$S_B = X_2 \overline{X}$$

k-map for RB

| 10r KB | \overline{\nabla}_2 \overline{\nabla}_1 \\ 00 | ₹ <sub>2</sub> X <sub>1</sub> | X <sub>2</sub> X <sub>1</sub> | X <sub>2</sub> X̄ <sub>1</sub> |

|--------|-----------------------------------------------|-------------------------------|-------------------------------|--------------------------------|

| AB 00  | X                                             | X                             | X 3                           | 0                              |

| ĀB 01  | 1.                                            | 0 5                           | 0 7                           | 0 6                            |

| AB 11  | 0 12                                          | 1 13                          | 0                             | 0 14                           |

| AB. 10 | X <sub>8</sub>                                | x,                            | X 11                          | 0 10                           |

$$R_{B} = \overline{AX}_{2}\overline{X}_{1} + A\overline{X}_{2}X_{1}$$

E-map for Z

| Y <sub>2</sub> X | $\overline{X}_2\overline{X}_1$ | ₹ <sub>2</sub> X <sub>1</sub> | X <sub>2</sub> X <sub>1</sub> 11 | X <sub>2</sub> X̄ <sub>1</sub> 10 |

|------------------|--------------------------------|-------------------------------|----------------------------------|-----------------------------------|

| AB,              | 0 0                            | 0 1                           | 0 3.                             | 0 2                               |

| ĀB 01            | 0 4                            | 0 5                           | 0 7                              | 0 6                               |

| AB 11            | 0 12                           | 0 13                          | 0 15                             |                                   |

| AB 10            | 0 .                            | 1                             | 1                                | 0 10                              |

$$Z = A\overline{B}X_1$$

Figure 4.28 Logic diagram

Example 4.6: Design an asynchronous circuit that has two inputs  $x_1$  and  $x_2$  and one output Z. The circuit is required to give an output whenever the input sequence (0,0) (0,1) and (1,1) received but only in that order. Design it using T flip-flop.

### Solution:

Given that  $x_1$  and  $x_2$  are inputs and Z is the output.

If the sequence (0,0) (0,1) and (1,1) arrives Z=1

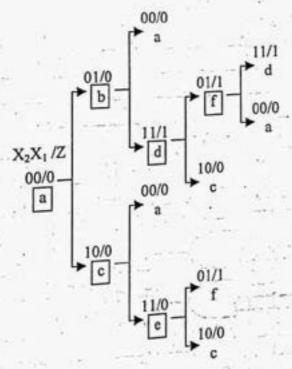

Otherwise Z=0

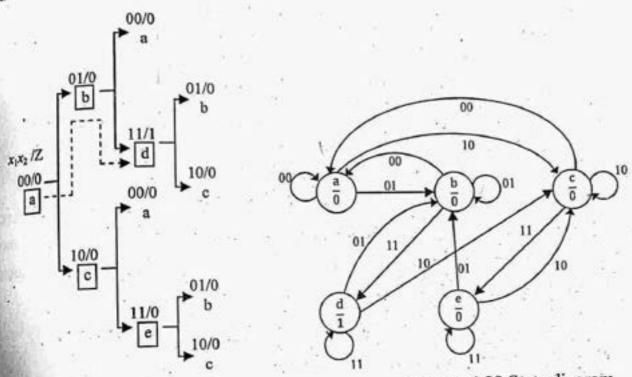

### Step 1: Draw the state diagram

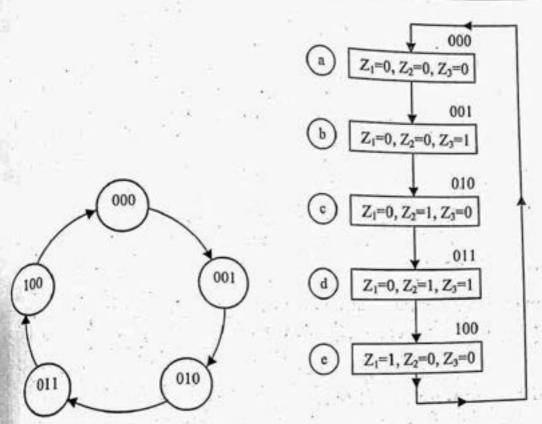

The state diagram can be easily drawn by using the following diagram shown in figure 4.29. Initially assume  $x_1x_2=00$  and output Z=0. The input  $x_1x_2=00$  can

change to  $x_1x_2=01$  or  $x_1x_2=10$ . Proceed the steps and assign states. Also highlight new states. The output will be Z=1 if the sequence (0,0) (0,1) and (1,1) arrives. So state 'd' has output 1. Now the state diagram can be easily drawn by using the figure 4.29 as shown in figure 4.30.

Figure 4.29

Figure 4.30 State diagram

Step 2: Construct the primitive flow table

| Present state | Next state, Output Z |                |                |                |  |

|---------------|----------------------|----------------|----------------|----------------|--|

|               | $x_1 x_2 = 00$       | $x_1 x_2 = 01$ | $x_1 x_2 = 11$ | $x_1 x_2 = 10$ |  |

| a             | (a), 0               | b,-            |                | С,-            |  |

| b             | a,-                  | <b>b</b> , 0   | d,-            |                |  |

| c             | a,-                  | 57.            | e,-            | ©,0            |  |

| d             | -,-                  | b,-            | @1             | · c,-          |  |

| e             | -,-                  | b,-            | (e) 0          | c,-            |  |

Table 4.32 Primitive flow table

Step 3: Reduce the primitive flow table

The primitive flow table can be minimized by merging the states 'a', 'b' and 'd' to a single state 'So'

$(a, b, d) \rightarrow S_0$

Also we can merge the states 'c' and 'e' to a single state 'S1'

$$(c, e) \rightarrow S_1$$

| Present state    | I                                 |                    | , Output Z         |                   |

|------------------|-----------------------------------|--------------------|--------------------|-------------------|

| Present state    | x <sub>1</sub> x <sub>2</sub> =00 | $x_1 x_2 = 01$     | $x_1 x_2 = 11$     | $x_1 x_2 = 10$    |

| S <sub>0</sub>   | (S <sub>0</sub> , 0               | S <sub>0</sub> , 0 | S <sub>0</sub> , 1 | S <sub>1</sub> ,- |

| . S <sub>1</sub> | S <sub>0</sub> ,-                 | So,-               | (S), 0             | · (Si), 0         |

Table 4.33 Reduced primitive flow table

Step 4: Assign binary values to the states based on race free state assignment.

Since there are two states, assign  $S_0=0$  and  $S_1=1$ . Also assign the unfilled near states as initial state '0'. Let the present states be A and the next state be  $A^+$ . Since the present states and next states differ by single bit, the circuit for the flow table shown in table 4.33 will be free from races.

| Present state | 1                                 | Next state A   | A+, Output Z   |                |  |

|---------------|-----------------------------------|----------------|----------------|----------------|--|

| A             | x <sub>1</sub> x <sub>2</sub> =00 | $x_1 x_2 = 01$ | $x_1 x_2 = 11$ | $x_1 x_2 = 10$ |  |

| 0             | 0,0                               | 0,0            | 0,1            | 1,-            |  |

| 1             | 0,-                               | 0,-            | 1,0            | 1,0            |  |

Table 4.34 State assignment

#### Step 5: Find output table

By using the T flip-flop excitation table shown below. Plot the output table.

| A  | A <sup>+</sup> | TA |

|----|----------------|----|

| .0 | 0              | 0  |

| 0  | 1              | 1  |

| 1  | 0              | 1  |

| 1  | 1              | 0  |

Table 4.35 Excitation table of T flip-flop

| Present state | Flip-flop inputs TA, Output Z |                                   |                                   |                |

|---------------|-------------------------------|-----------------------------------|-----------------------------------|----------------|

| A             | $x_1 x_2 = 00$                | x <sub>1</sub> x <sub>2</sub> =01 | x <sub>1</sub> x <sub>2</sub> =11 | $x_1 x_2 = 10$ |

| 0             | 0,0                           | 0,0                               | 0,1                               | 1,-            |

| 1 .           | 1,-                           | 1,-                               | 0,0                               | 0,0            |

Table 4.36 Output table

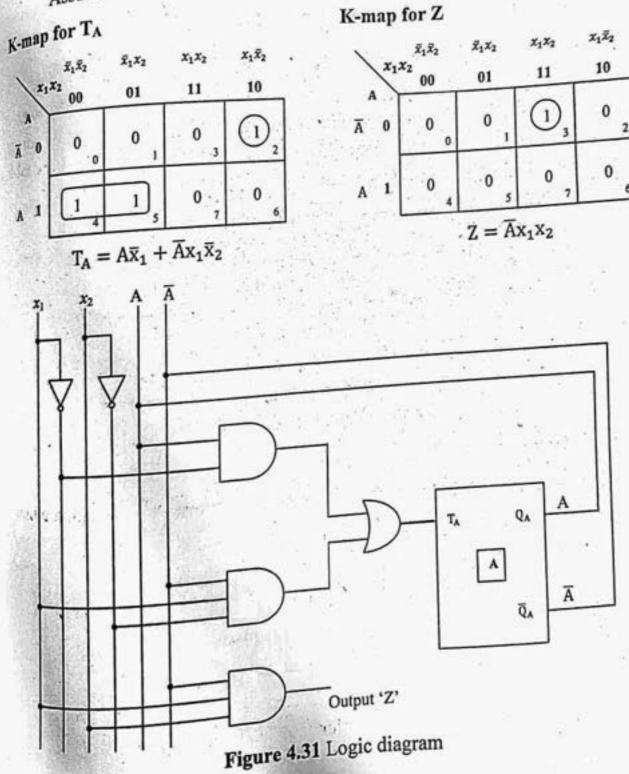

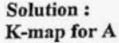

Step 6: Find the flip-flop input equations and output equations using K-map. Assume '0' for unspecified flip-flop inputs and unspecified outputs.

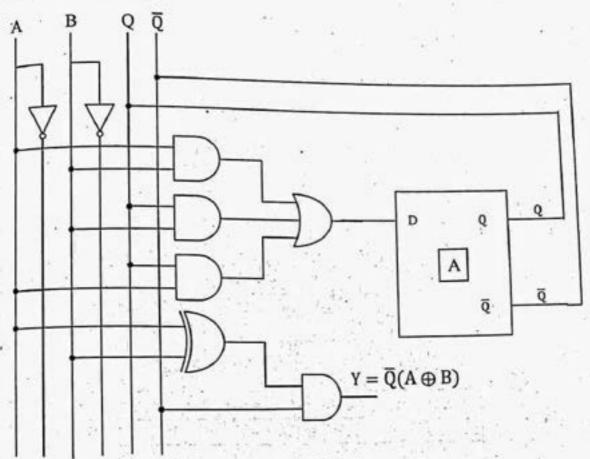

#### Example 4.7: Design a T flip flop using logic gates.

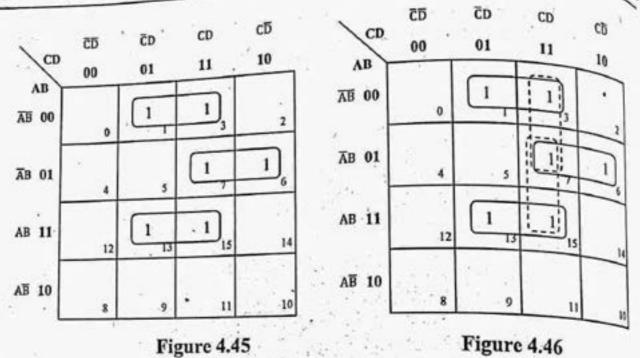

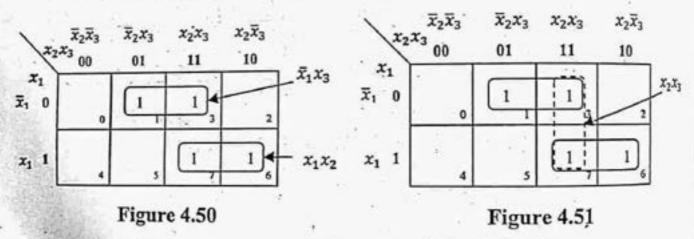

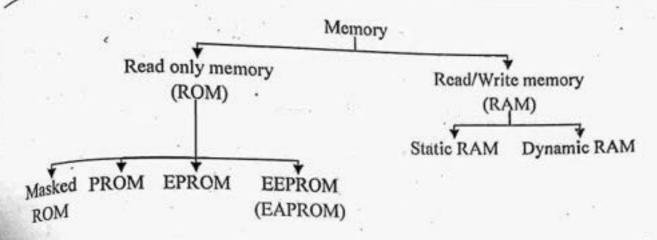

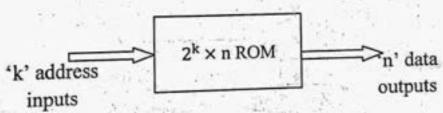

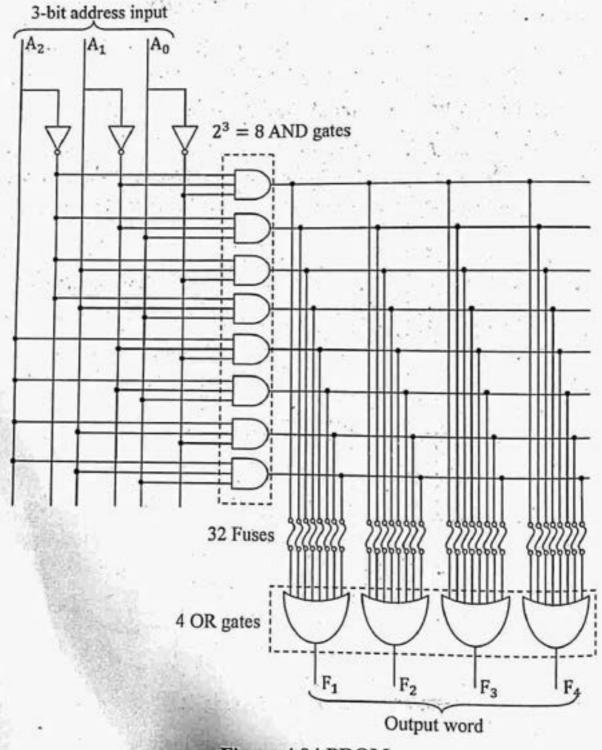

#### Solution: