SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Applications Instrumentation Amplifier: \* In a humber of industrial and Consumer applications, one is required to measure and control Physical

quantitées measured with the help of transduc

The output of transducer has to be amplified so that it

can drive the indicator.

\*This function is Perfored by an instrumentation amplifier.

The important features are

- high gain accuracy

- high CMRR

-> high gain Slability with low temperature coefficient.

-> low De Offset

-> low output impedame

op-amps MA725 to meet above requirements. Available op-amps are AD521, AD524, AD620, AD624

red

WE

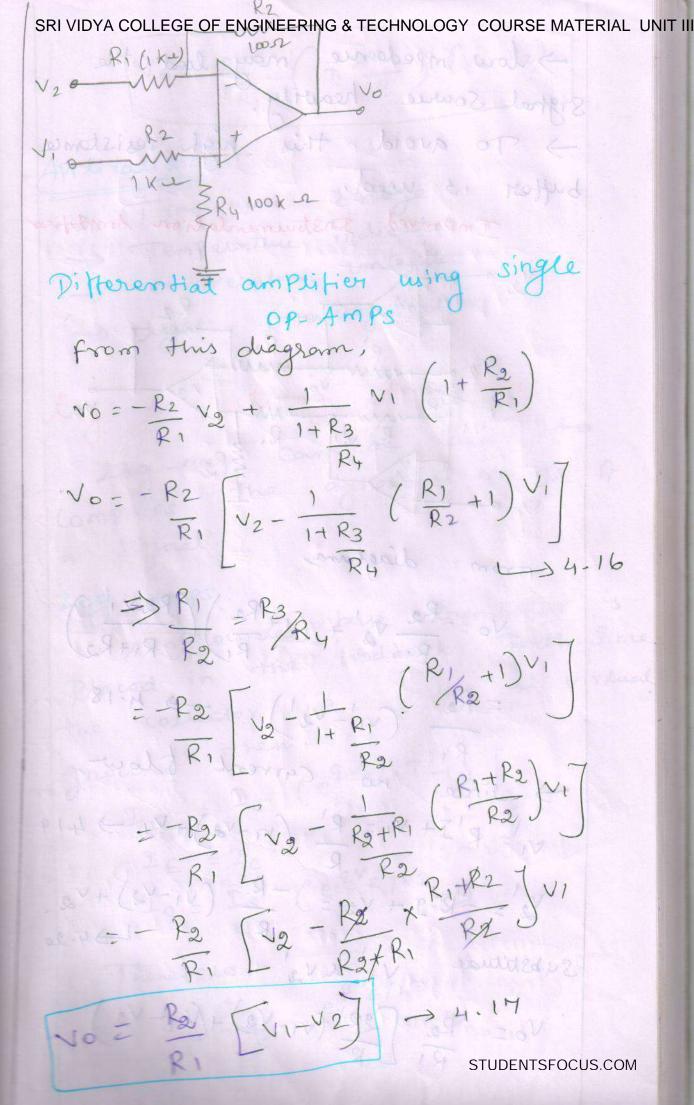

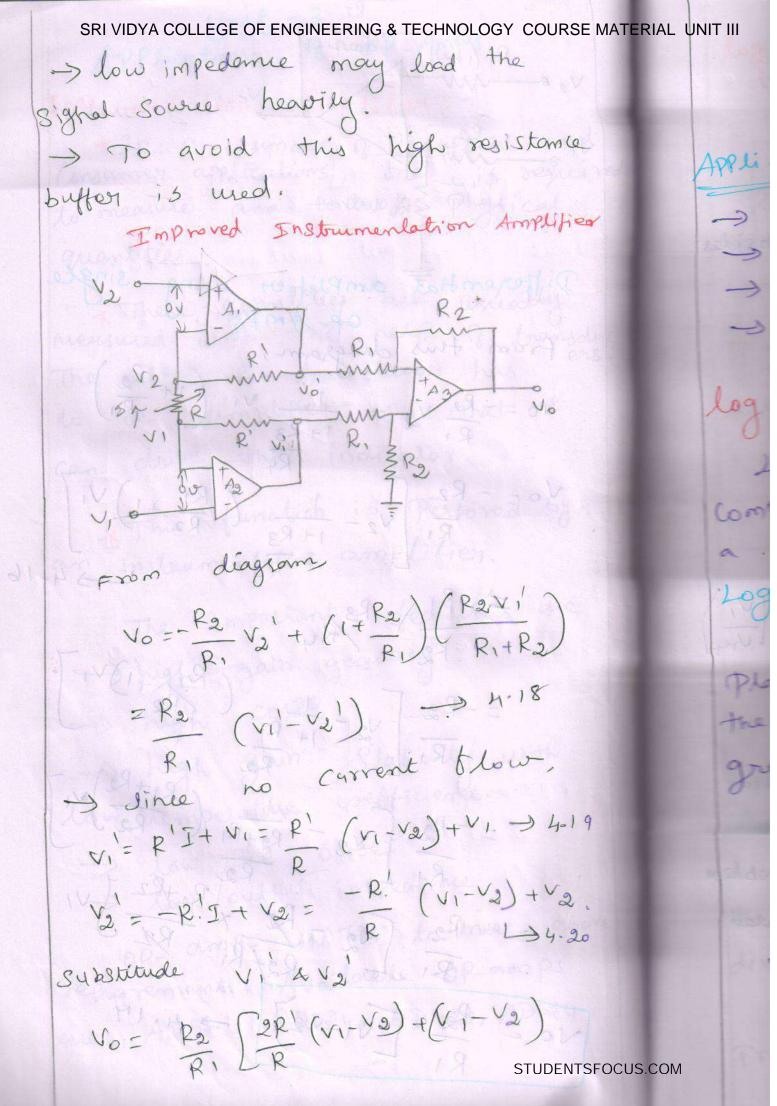

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Vo = R2 (1+ 2R1) (V1-V2) Applications! Transduces bridge

Temperature indicator

Temperature controller

Hemperature controller

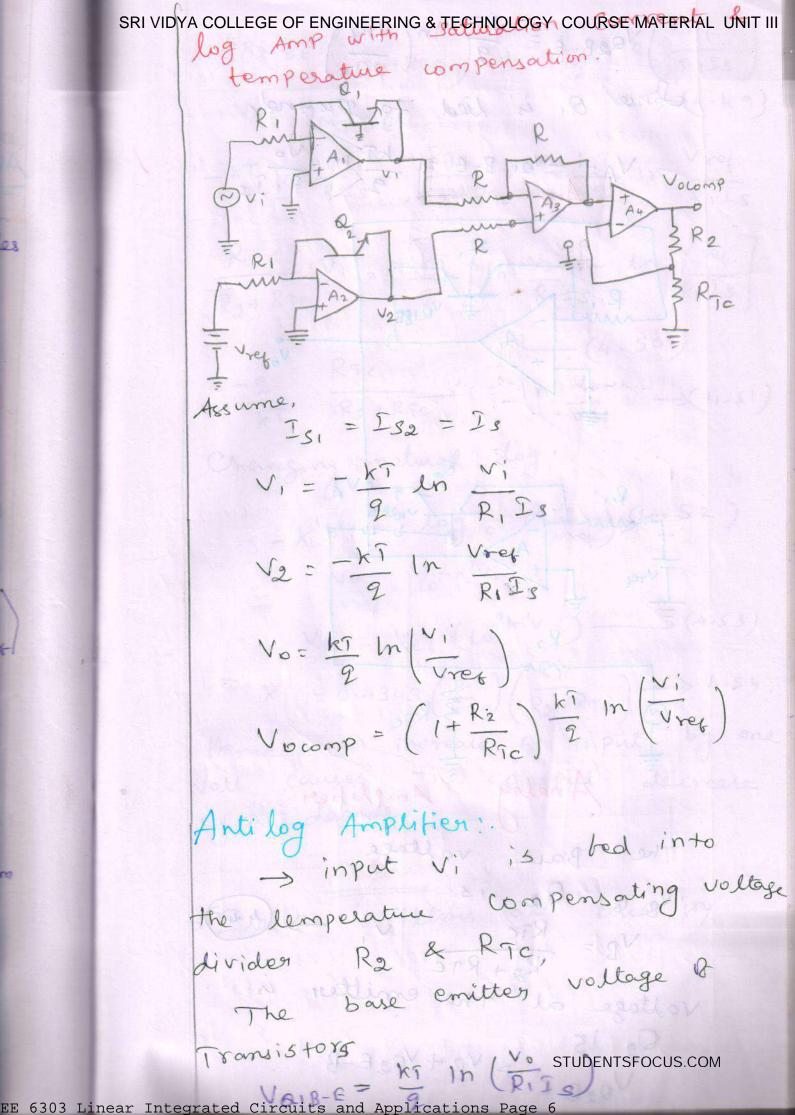

Jught intensity meter log & Antilog Amplifier: Log-amp can be used to Compress the dynamic range of A grounded base transistor is Placed in the feedback Porth. Since the collector is held at virtual ground then, ground

IE = IS (e<sup>2</sup>V<sub>E</sub>/KT-1) SE = SC Sc = Is (e<sup>2</sup> × 1 × 5 -1) Matagains and Malsonal out Therefole Ic = e endow-1) movies? STUDENTSFOCUS.COM

EE 6303 Linear Integrated Circuits and Applications Page 4

Hen

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III

$$e^{9VE/kT} = \frac{Ic}{Is}$$

$$= \frac{Ic}{Is}$$

$$= \frac{Ic}{Is} = \frac{1^3}{Is} \approx \frac{1^3}{Is} = \frac{$$

Taking natural log on both sides  $V_k = \frac{kT}{2} \ln \frac{Tc}{Ts}$

Soi  $-k\bar{l}$   $\ln\left(\frac{V_i}{R_i\bar{l}s}\right) = -\frac{k\bar{l}}{2}\ln\left(\frac{V_i}{V_{ref}}\right)$

to transistor & with temperature

To overlome this Problem two transistors are integrated close together in the Same Silicon waber.

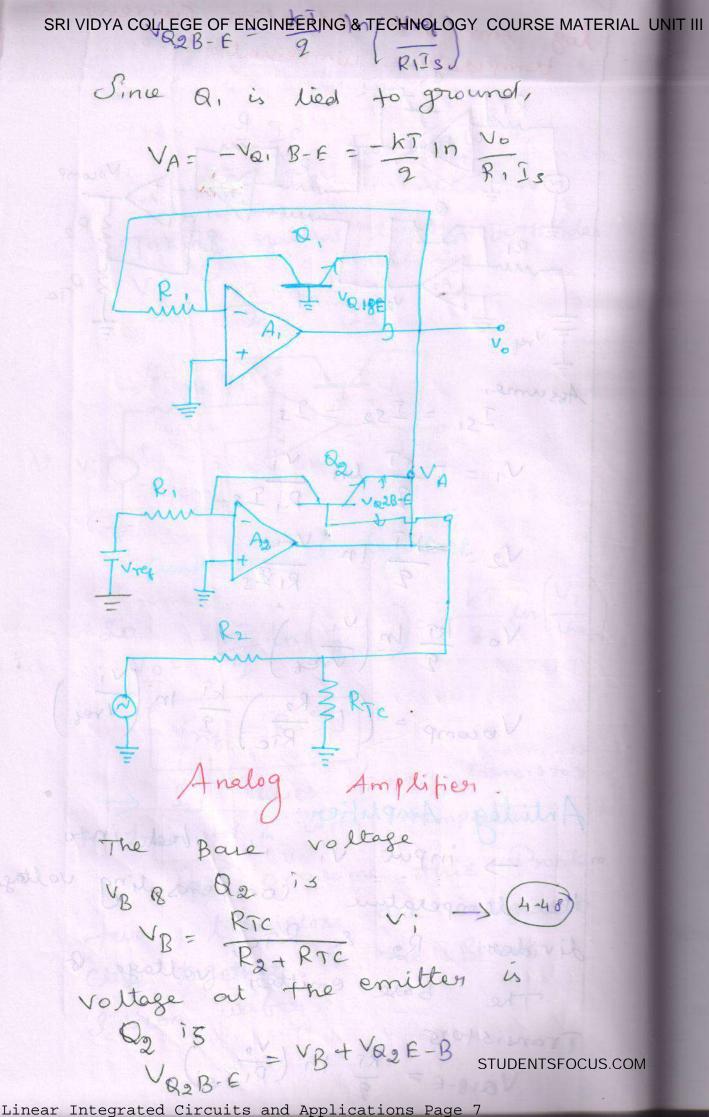

DLLEGE OF ENGINEERING  $\alpha$  120  $V_1 - \frac{R^4}{9}$   $1n\left(\frac{1}{R_1Is}\right)$  (4-49)SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY, COURSE MATERIAL UNIT III  $V_A = V_{Q,2} B.E$   $-\frac{kT}{2} \ln \frac{V_0}{R_1 I s} = \frac{R_1 c}{R_2 + R_1 c} V_1 - \frac{k_1}{2} \ln \frac{V_{ref}}{R_1 I s}$   $V_{20}$ RTC V; = -kT (In Vo - In Vret | RIIs Rg+ RTC L (4.50) -2 RTC V; = In Vo ->(4.51) Changing natural log, - k'V; = log 10 (Vo Vrey) (4.52) Vo Vyer = Lo-K'V; Vo = Vef (10 k'v;) - 3 (4.53)  $k' = 0.4343 \left(\frac{9}{kT}\right) \left(\frac{RTC}{R_0 + RTC}\right) \longrightarrow 4.54$ Hence an increase of input by one volt causes the output decrease by a decade. > Electric filtons are used in

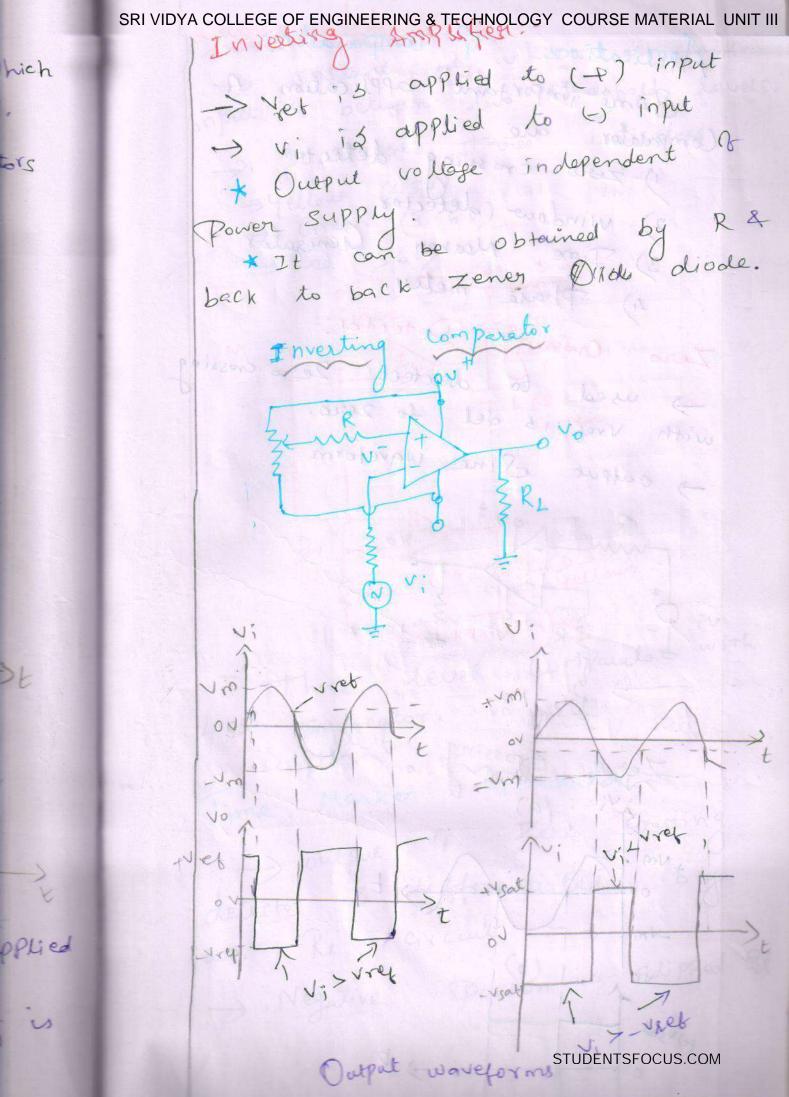

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III proparato TS. A Comparator is a circuit which signal voltage applied. 2) soverting comparator input & v; to (4) input. > It -Vsat for v; Lvrer & STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III A Comparator: Applications Some important application 17 Comparator are 1) zero crossing detector 2) Window detector 1 Doub 3) Time Marken Generator 4) Phorse meter Zero Crossing Detector: ) used to dectect Zero crossing with vrey is del to zero. -) output Sine waveform VO (e) Vsal STUDENTSFOCUS.COM

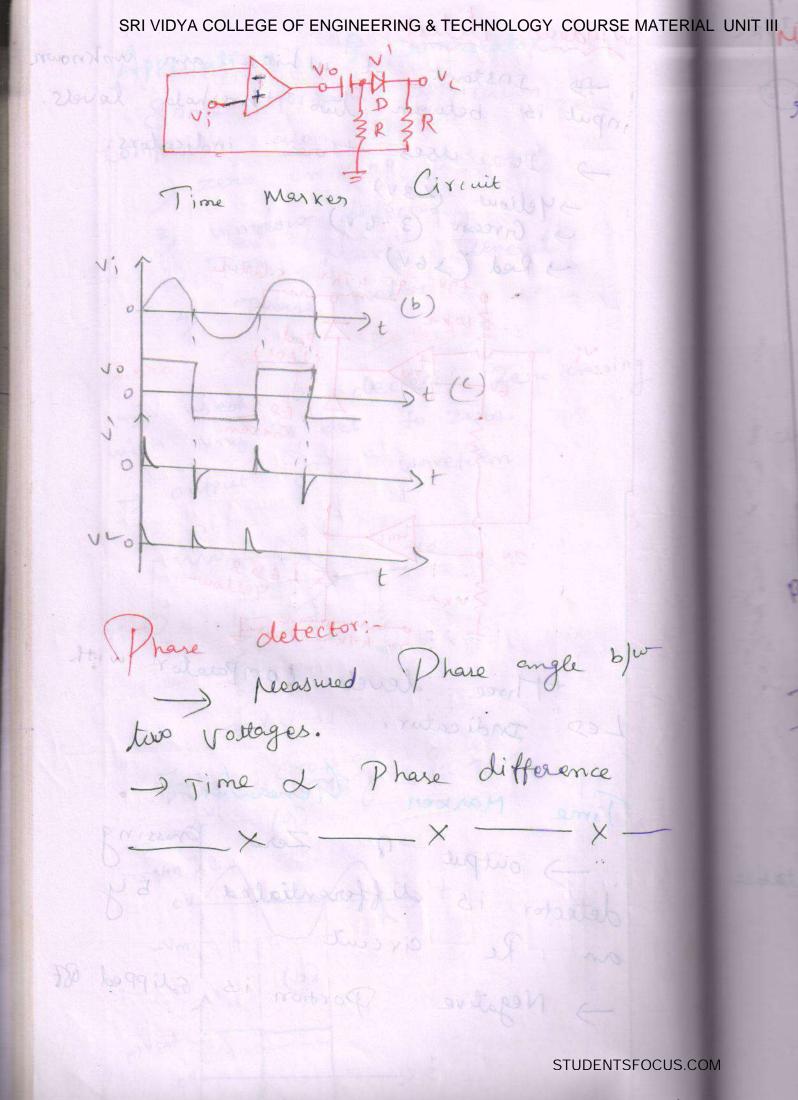

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III ) Instant at which am unknown input is between two threshold levels. -) It uses those indicators. y Green (3-6 V) I Red () 6V) 47K2 5.6K2 devel comparator with Indicator. Generator: Marken -> output ? Zero Crossing detector is differentiated by an Re circuit -> Negative Portion is clipped 87 STUDENTSFOCUS.COM

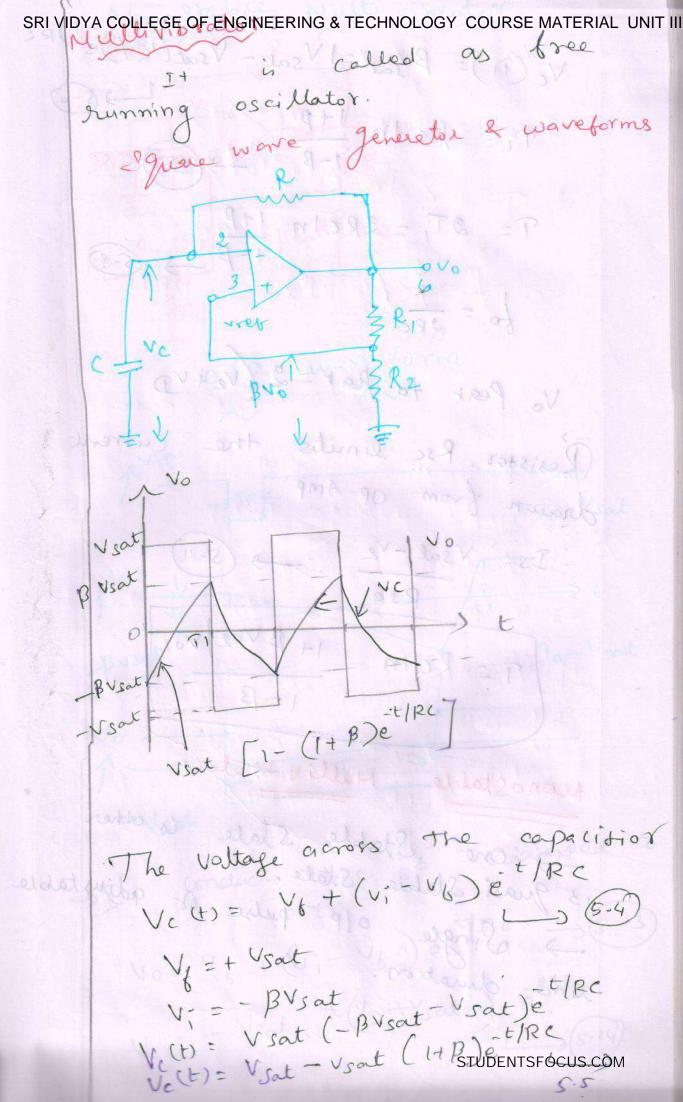

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Vc(TI)= Byat = Vsat - Vsat (1+B)e  $T_1 = Rc \ln \frac{1+\beta}{1-\beta} \longrightarrow (S-7)$ T= 2T, = 2RcIn 1+13

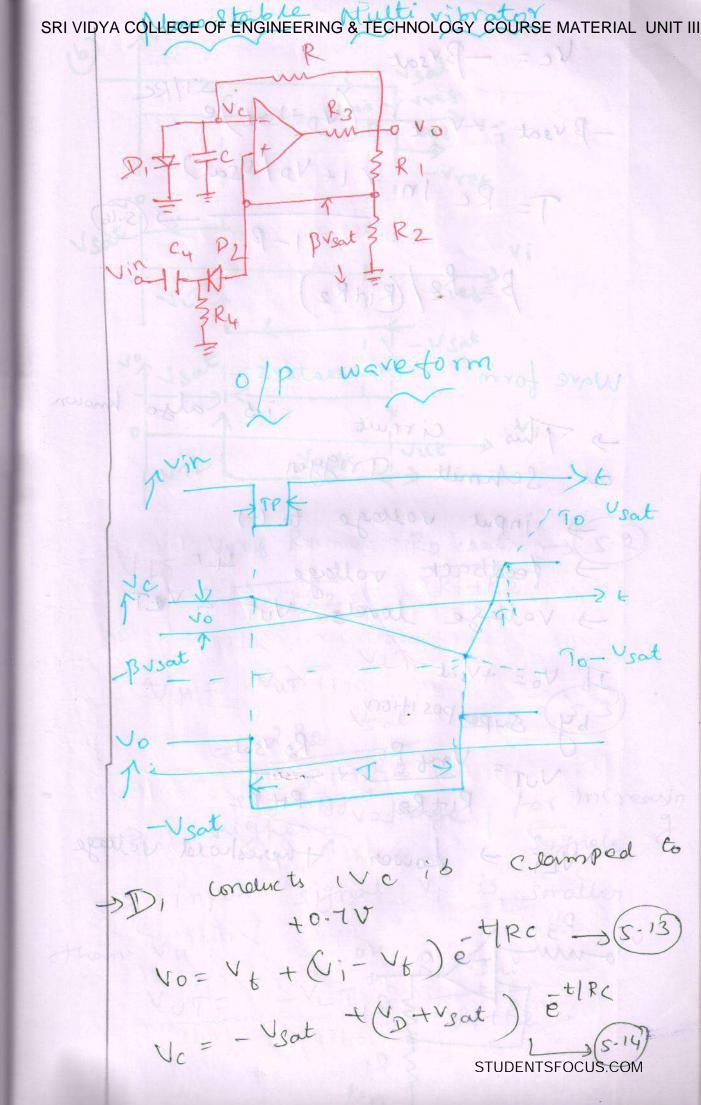

1-B - 5-8 to = 1 Vo Peak to Peak = 2 (V2+VD Resistor Rsc limits the Cyrrent drawn from OP-AMP T= RCIN 1+ BV02/V01 1-B monostable Multivibrator: ) one Stable State to other Jingle of pulse or adjustable time duration. (2) 3 quasi Stable State. Sollov of (t): V sat (- Preat - V sat)e

EE 6303 Linear Integrated Circuits and Applications Page 16

MRC

able

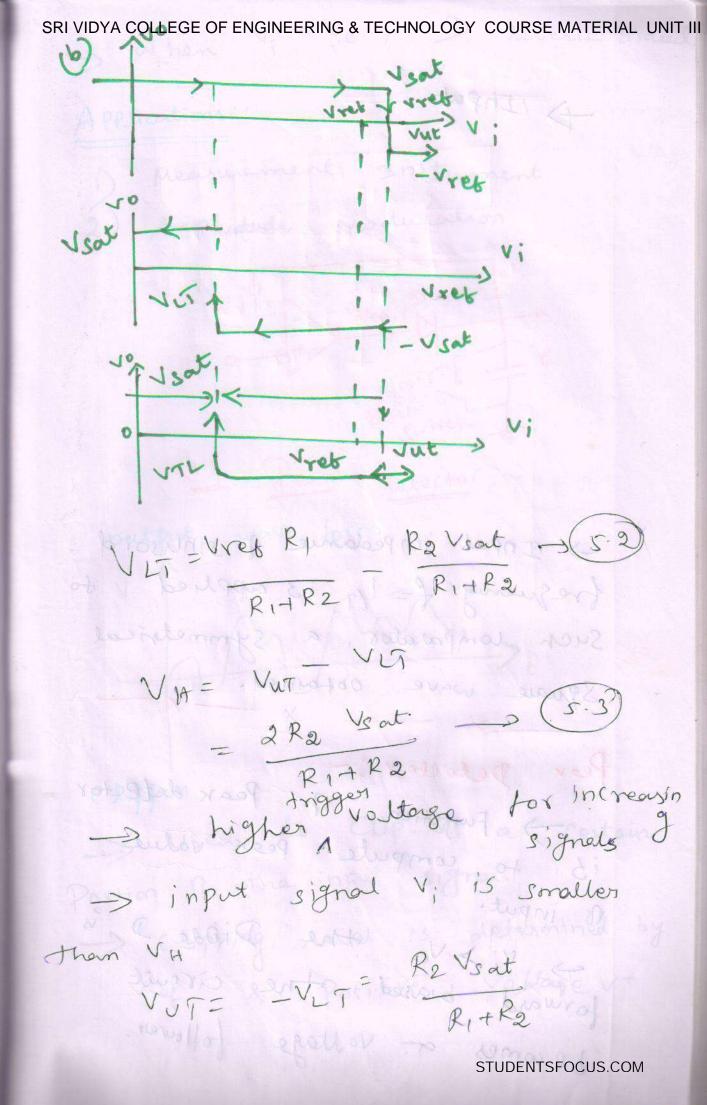

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT JII Vc = - BYsat -BVsat = -Vsat + (VD+Vsat)e T/RC T= Rc In (I+ VD/Vsat) B= R2/(R1+R2) Wave form henceators: -> This circuit as Schmitt Trigger > input voltage to (-) -) feedback voltage 4' - J Vollage levels VuT & VIET If Vo= + Vs at by Superposition VUT = Very R, Re Vsat

RITRE RT R2 NITO Lower threshold voltage 5 Thory & RIV STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Input impedance of sinusoid frequency f= 1/7 is applied to Such comparator, a symmetrical Square wave obtained. Peax Detector: - Peax detector

- Function to compute peak value Of input. > V; > Vo the Diode D forward biased, the cirruit voltage follower. be comes a STUDENTSFOCUS.COM

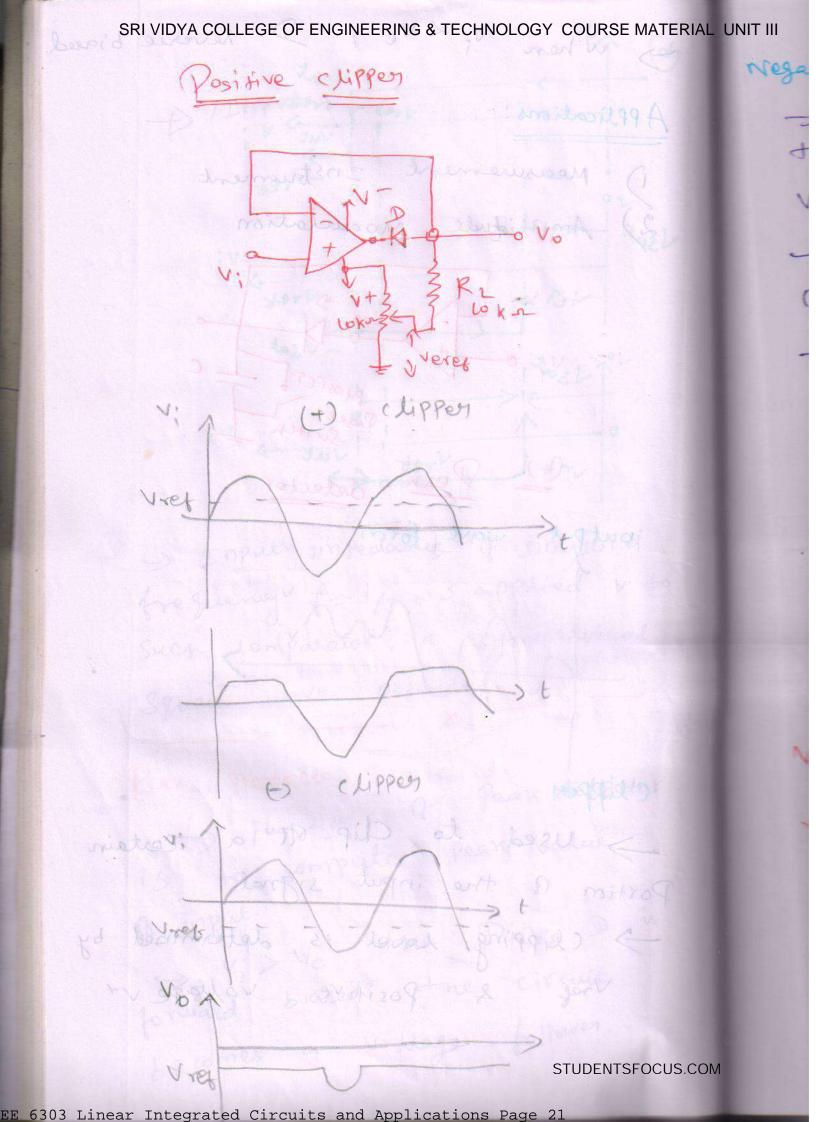

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Applications: Measurement Instrument 2) Amplitude modulation but put wave form Clipper > used to Clip- of a cortain Poition 18 the input signal. -> Clipping hevel is determined by Viet & Positive vollage v+ STUDENTSFOCUS.COM

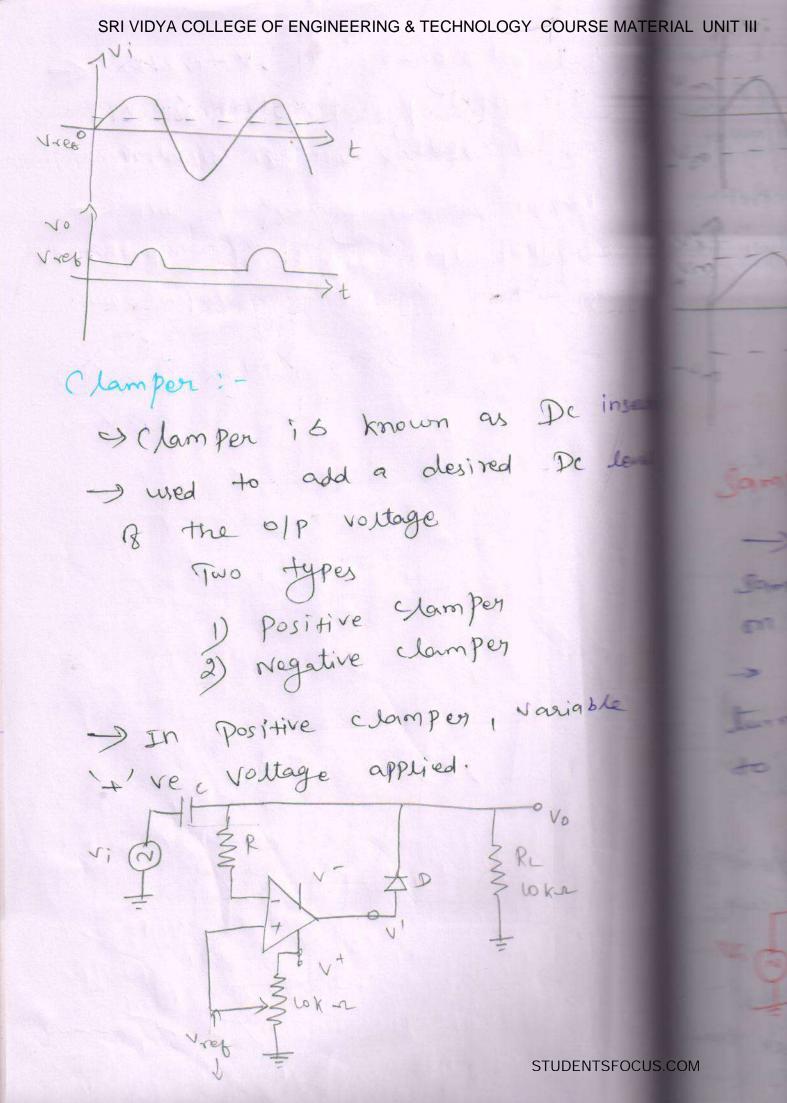

CLIPPEY: -Negative The Polarity of the reference voltage Vref. clips regative parts -> It of the input signal of set voltage Vret.

EE 6303 Linear Integrated Circuits and Applications Page 24

level

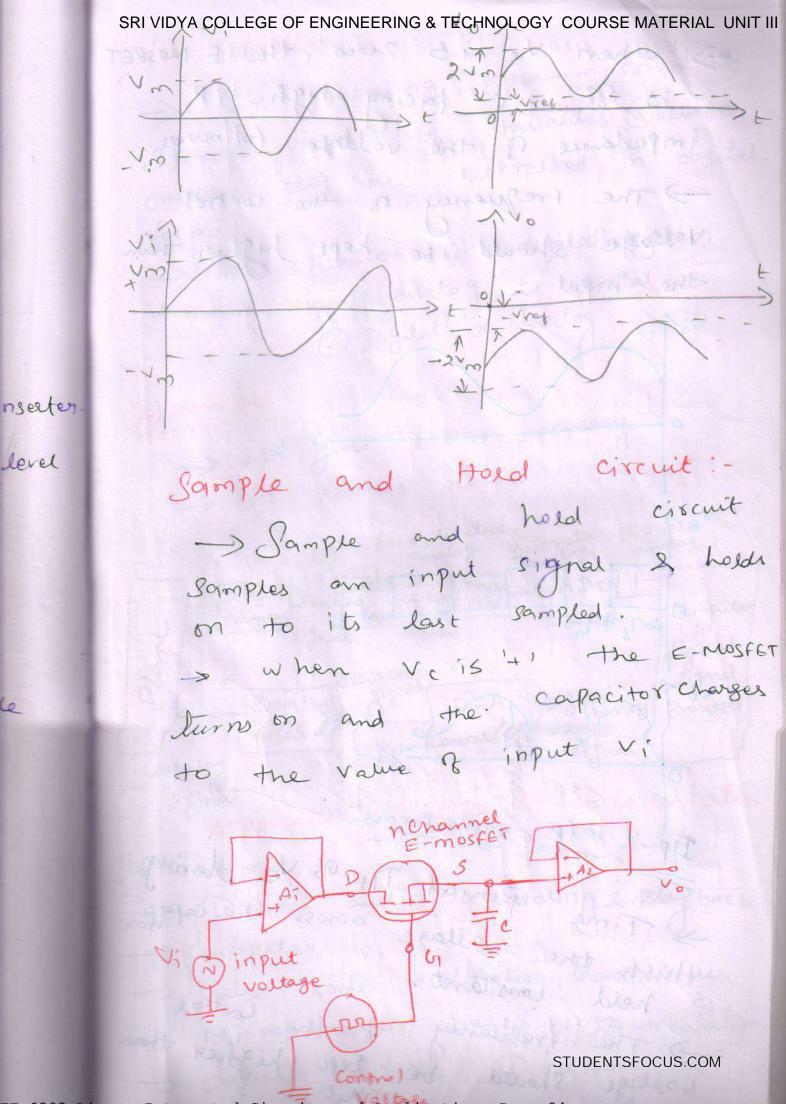

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III > when Ve 15 2000, the E MOSFE 13 088, c lacing high ilp > F Impedance of the voltage follower Storas Carre -) The frequency of the control for m. Voltage should be kept higher than -> 7 the input 15 ba single and thereby algoria · Los to the or the Talzona > atta) 104/9ative V waste to their me or TIP & OIP wave forms: > Time pourod TH Ob Ve during which the voltage across the capacitor is held constant. -> The frequency of the Control voltage should be kept higher than EE 6303 Linear Integrated Circuits and Applications Page 25

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III DIA Converter -> For Processing transmission SEET Storage purpose the variables (vollage, current etc) are expressed in digital form. -> The operation of digital system 15 based upon @ analog to digital Digital to analog. -> It gives better accuracy -9 It reduces noise Analog Band limited Discrete Discrete Sensor J Antialis J Sample J ADC J Transpler signal Smoothin Signal D-Digital processor PAID & D/A converter Application shop & 86 182 Jah a APPLications: -> Digital audio recording & playback -> Computer -> pulse lode Modulation transmission > Microprocessor based instrymentation han -> digital Signal Pristablisher COM

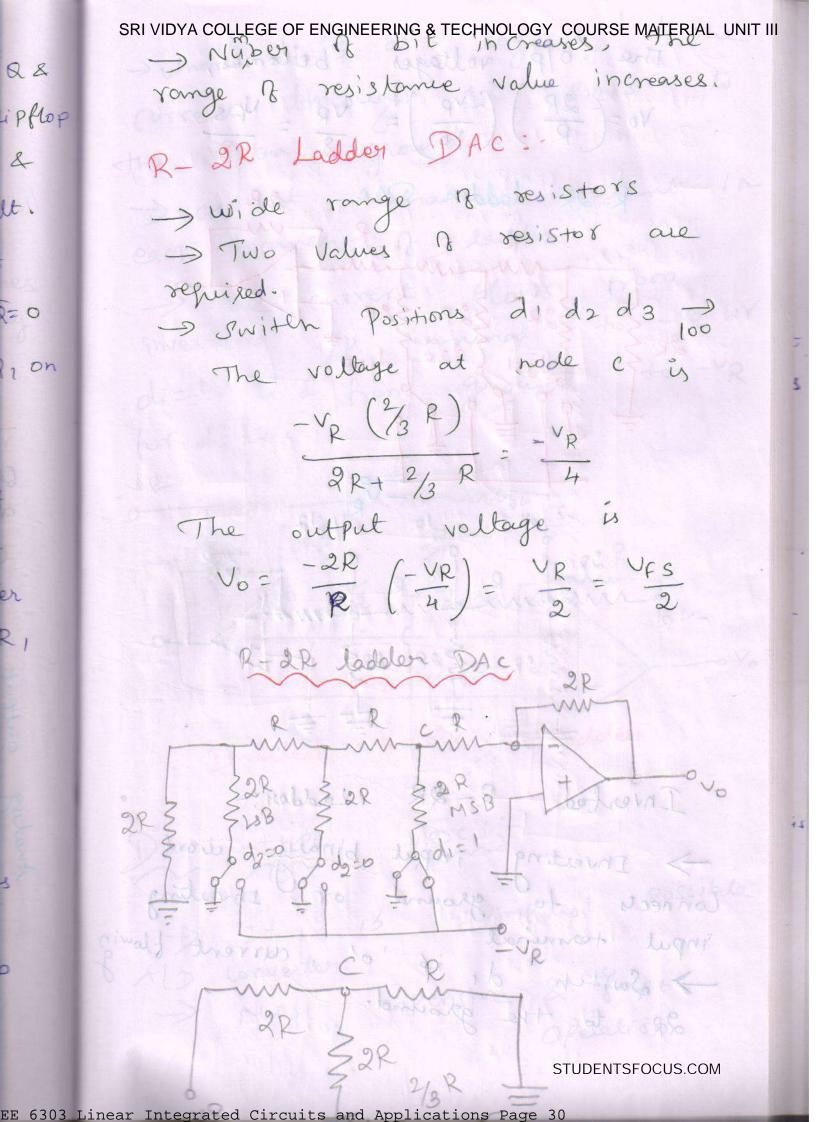

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III There are Three techniques, ) weighted resistor DAC 2) R-2R ladder 3) Inverted R-2R ladder Weighted Resistor: -> It how n electronic. dida...dn controlled by input word. -> It the input bit is o the Switch connects the resistor to the ground. ava 30, Io = 21+ I2 - + In DY 32R 32R 32R 32R a dolsB) a d3 & pd2 pp +> d, (MSB) VR (di2+ d2+--+dn Olp voltage STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III DIE working as a curren voltage (onverter -> Reference voltage should be +51 & olp will be negative > On resistor must be very low & they should have Zero Offset voltage. -> Different types of digitally Controlled SPDT electronic Switches quailable of which & two are Connected as shown in Figure - The Bulling 4 spelloy wiferar in Krattod STUDENTSFOCUS.COM

EE 6303 Linear Integrated Circuits and Applications Page 28

nes

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III -> two Complementary gate inputs Q & Q Come from NOSFET S-R Priphs Low -> logic'' lorresponds to - LOV & logic'o' corresponds to zoro volt. -> If there is '1' in the bit line S=1 & R=0, Q=1 & Q=0 > This drives the transistor 910 -> -VR means transistor as remains 86.

Remains 86.

Remains Res transistor R. 187 & Q2 on.

The output & CMOS inverter is at logic 1, ie 5 v applied to R, through voltage follower R-2R / ladden / DAG J-Disadvantages: > wide range of resistor values required. -> For better resolution, the 11P binary word length has LO be in created.

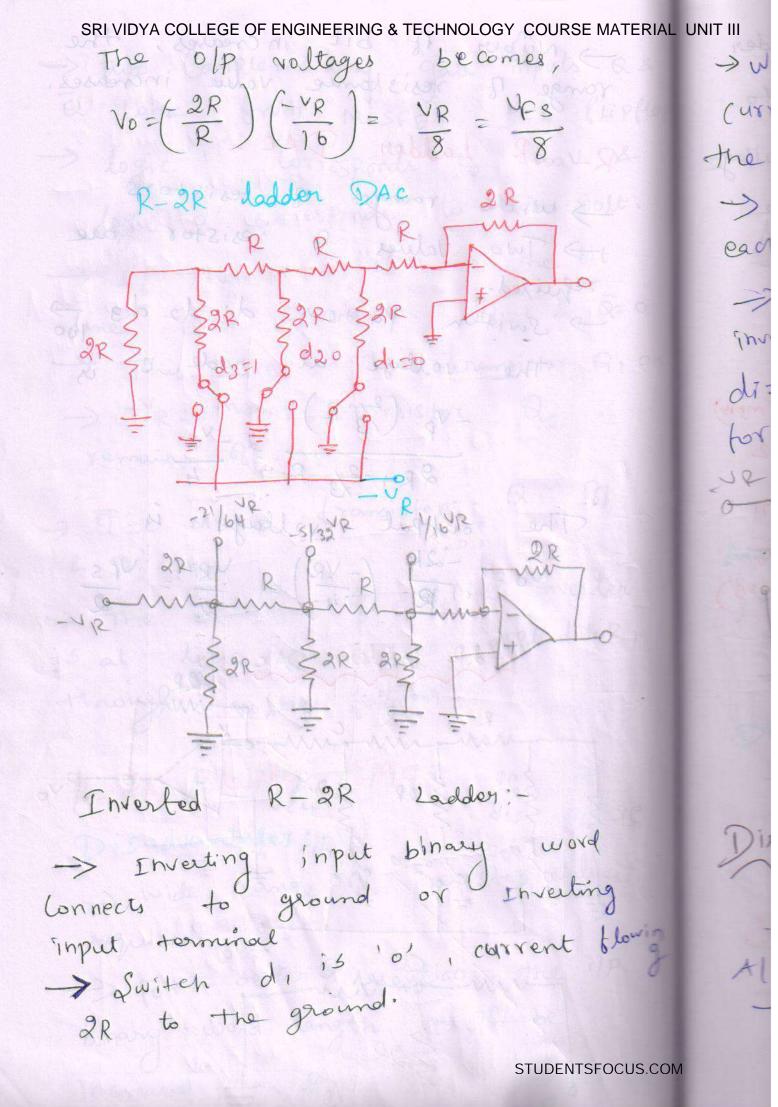

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Current through 2R Sinks to the viv tual ground was end 8 > current remains constant in each branch of ladder -> The current flows from investing ip terminal di=1, 02 from ground to -VR for d; = 01 32R 288 Inverted R-2R ADC'S :possible STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III -> Consists of a resistive divider network 8 op-900P, 8 line to 3 line en coder. - to compare the the va with each 8 +VR CRef. voltage X6 X 5 Advo X3 X2 No vollage input va svd Va 2 Vd Previous Valustudentsfocus.com

EE 6303 Linear Integrated Circuits and Applications Page 33

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III ler HE 128 1 Applications: - land 10 did manto Instrumentation where Speed is important -) data loggers -> digital meters > runitoring systems D) Panel meters -> typical Conversion time is un Advantages: 30) of less -> Conversion time is limited Disadvantages: > the number of Comparators required almost doubles for each bit. -> Mose Complex Successive Approximation Converter => Eight bit Converter require 8 clock Pulse to obtain a digital ofstudentsfocus.com

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III > SAR required value of each bit by trial & error. -> Sets the MSB di = 1 with all Other bits '0', trial lode is 10000000 Joseph Jeok DAC provening Hima it limited the Functional Diagram DAC OIP Vol then JE Va < DAC OIP the 100000000 25672 one conversion Actual signal to STUDENTSFOCUS.COM EE 6303 Linear Integrated Circuits and Applications Page 35

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III -) Reset MSB to 0 2 go on to the next lower Significant bit el rabagest m 2 mis port (greet digital SAR OIP Comparator 11 Representation 0000 10000000 11010100 11000000 11100000 110100000 SATA1 1000 1 pring 6110000 110101000 donate 11010110 .000 11010101 11010100 Integrating type of ADC'S > Do not require as ) H circuit at > Input Changes, ADC 01P Code will be 2 value of input averaged Over the integration poulod. Marge balancing ADC: > Covert input signal to a frequency -> output code of to analog input -> output VIF conventer depends apon om Rc Product Drawback: Charge balancing ADC STUDENTSE STUDENTSFOCUS.COM

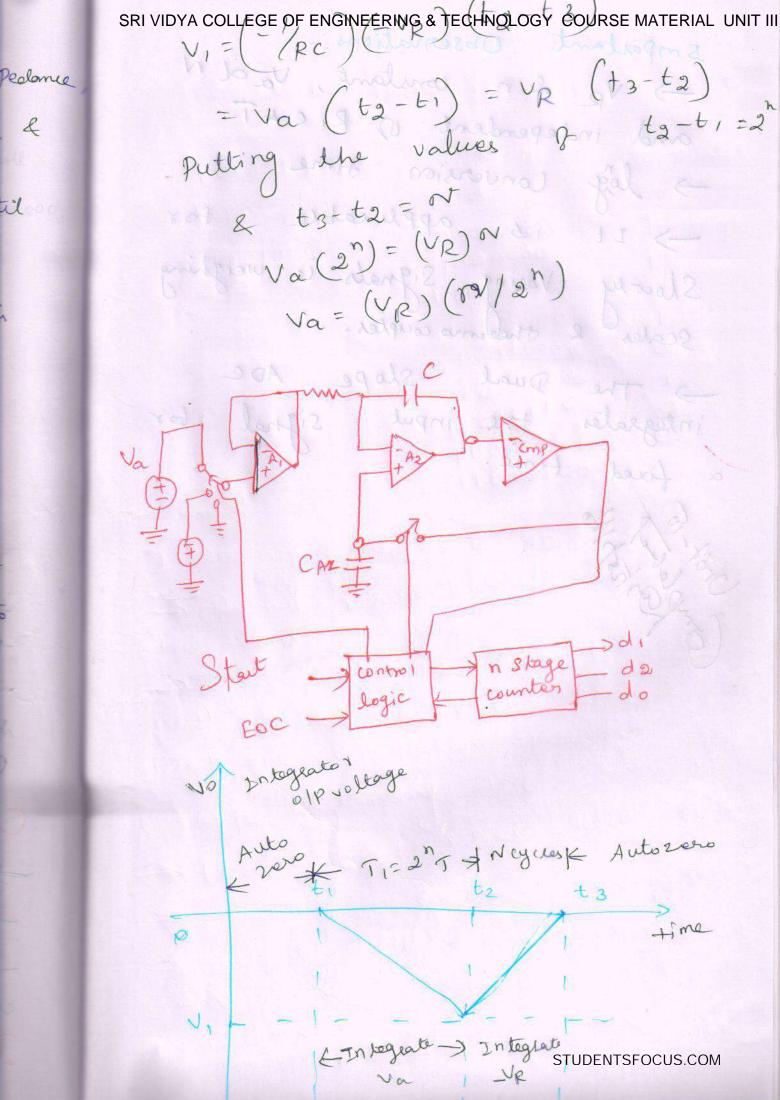

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Slope - consists or high input impedance buffer A, Precision integrator A2 & Voltage comparator. -> VR is opposity Polarity until the integrator OIP is zero. -> Brarro, othe Switch Sw, i Connected to ground, Swy is Close. -> CAZ Provides Automatic Compensation. > Lounter resets itself to zero at the end of the interval T, & the switch sw, is connected to Change, (-VR). Analog input vollage

Va. Tiz ta-tiz 2 counts clock vate t3-t2 z digital count N clock rate Integrator ator Avo = (-1/RC) VAt Vo= ( YRC) Va (f2-ti) STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III C Observations -> Vp & n constant, Va & N and independent of RICAT -> log Conversion time -> It is applicable for Showly Varing Signals is weighing Scales & Theormo couples. The Dual Slope ADC integrales the input Signal for a fixed time.

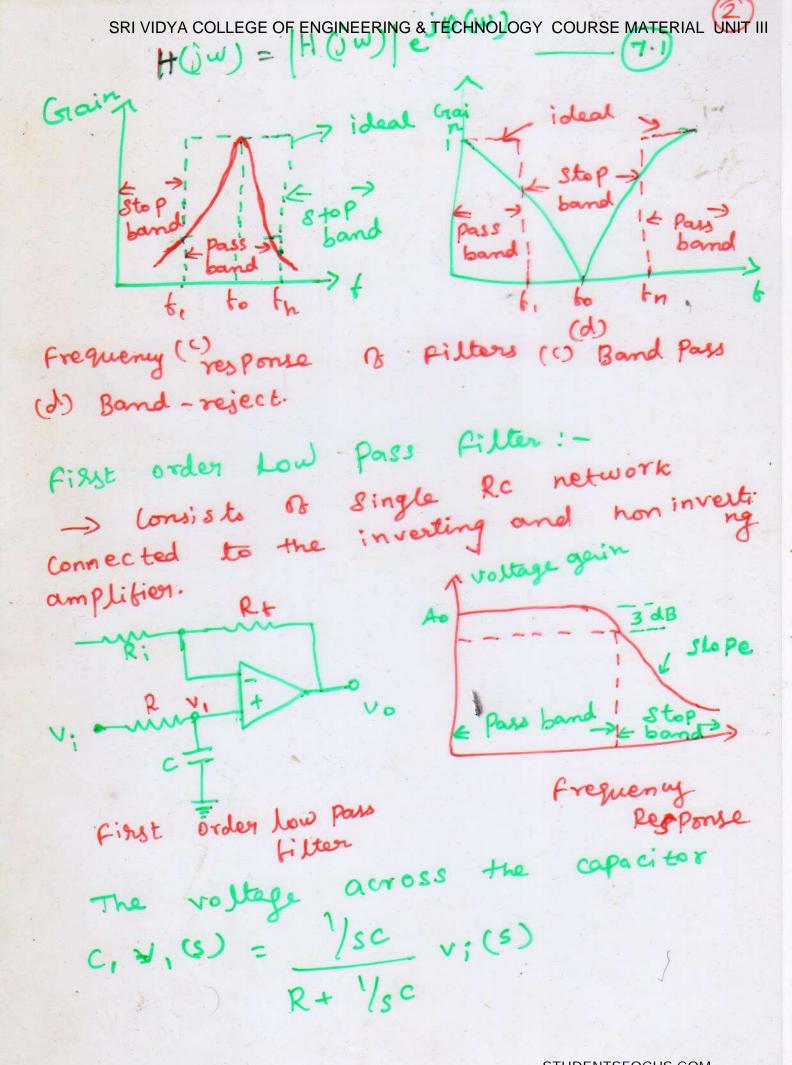

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III > Filters are used in Communication & signal processing and all electronic instruments. use op-amp as the active elements. & resistors and capacitors & capacitors as the Passive The Most Commonly used filters Clements. 2) High pass filter 3) Band Pass filter 4) Band Reject filter Frequency response of Pilters (a) Low paus (b) high pass filters. transfer function

(4(S) = Va(S)

Vij(S) under Steady state STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Rcs+1 v;(5) Closed Loop gain, A0 = 40 (5)  $\frac{V_1(S)}{V_1(S)} = \frac{1 + R_F}{R_1} \rightarrow \frac{7.5}{R_2}$  $H(s) = \frac{V_0(s)}{V_1(s)} = \frac{V_0(s)}{V_1(s)} \cdot \frac{V_1(s)}{V_1(s)} = \frac{A_0}{RCs+1} \rightarrow \boxed{7.6}$ Wh = /RC -> (7.7)  $H(S) = \frac{V_0(S)}{V_1(S)} = \frac{A_0}{S+W_h} = \frac{A_0W_h}{S+W_h} \rightarrow \frac{7.8}{S+W_h}$  $H(j\omega) = \frac{A_0}{1+j\omega Rc} = \frac{A_0}{1+j\omega Rc} = \frac{1}{1+j(t+1)} \rightarrow \frac{7.9}{1+j\omega Rc}$ th = / Rc 4 f = 00 2 11 very frequency & LLth | H(jw) | = A. f= 62' | H(iw) 1 << Ao = 0, it t>> th > Frequency range from 0 to 6h > pass band. -> \$>th Stop band STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Order Active filter: An improved filter response can be Obtained by using Second order Active filters. Vo= (I+ Re Ri) VB = AOVB -> (7.13) Ao = 1+ RF -> (7.14) Circuit Diagra A 427 VB kcl law, at A gives viy, = VA (41+42+43)- VOY3 - VB 42 = VA (41+42+43)-VOY3 - NOY2 -> (7.15) kce law at node 'B' is VA 42 - VB (42+44) = vo (42+44) VA = VO ( 42+ 44) A042 A04142 voltage gain = Vo = 4,42 + 44 (4,+42+43)+ 92 43 (I-As) STUDENTSFOCUS.COM

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III Se cond order Low Transfer function of low pass filler = H(s)  $H(S) = \frac{A_0}{S^2 c^2 R^2 + SCR(3-A_0)+1}$ 7.18 H(s) = Ao wh 2 2 52 d who who = gain Ao = upper cut of frequency

wh = upper cut of frequency

in radian/second d = damping welficient Wh= /RC -> 7.20 d: (3-A0) -> 7.21 Aο/ωη) + jd (ω/ωη) + 1 H (jw) =

SRI VIDYA COLLEGE OF ENGINEERING & TECHNOLOGY COURSE MATERIAL UNIT III

Normalized Expression for lew pass

H(jw) = 32 + d Sn+1

The expression of magnitude in dB

transfer function

Ao

20/2 (H(jw)) = 20/2

1-w2 )2+(dw/wh)2